RocketIO™ Transceiver User Guide www.xilinx.com 93

UG024 (v3.0) February 22, 2007

Other Important Design Notes

R

Other Important Design Notes

Receive Data Path 32-bit Alignment

The RocketIO transceiver uses the attribute ALIGN_COMMA_MSB to align protocol

delimiters with the use of comma characters (special K-characters K28.5, K28.1, and K28.7

for most protocols). Setting ALIGN_COMMA_MSB to TRUE/FALSE determines where

the comma characters appear on the RXDATA bus. When ALIGN_COMMA_MSB is set to

FALSE, the comma can appear in any byte lane of RXDATA in the 2- and 4-byte primitives.

When ALIGN_COMMA_MSB is set to TRUE, the comma appears in RXDATA[15:8] for the

2-byte primitives, and in either RXDATA[15:8] or RXDATA[31:24] for the 4-byte primitives.

(See “ALIGN_COMMA_MSB,” page 67.)

In the case of a 4-byte primitive, the transceiver sets comma alignment with respect to its

2-byte internal data path, but it does not constrain the comma to appear only in

RXDATA[31:24]. Logic must be designed in the FPGA fabric to handle comma alignment

for the 32-bit primitives when implementing certain protocols. (Note that FPGA logic is not

required for 1-byte and 2-byte configurations.)

One such protocol is Fibre Channel. Delimiters such as IDLES, SOF, and EOF are four bytes

long, and are assumed by the protocol logic to be aligned on a 32-bit boundary. The Fibre

Channel IDLE delimiter is four bytes long and is composed of characters K28.5, D21.4,

D21.5, and D21.5. The comma, K28.5, is transmitted in TXDATA[31:24], which the protocol

logic expects to be received in RXDATA[31:24].

Using Table B-1, page 135, and Table B-2, page 143, the IDLE delimiter can be translated

into a hexadecimal value 0xBC95B5B5 that represents the 32-bit RXDATA word. On the

32-bit RXDATA interface, the received word is either 32-bit aligned or misaligned, as

shown in Table 2-24. In the table, “pp” indicates a byte from a previous word of data.

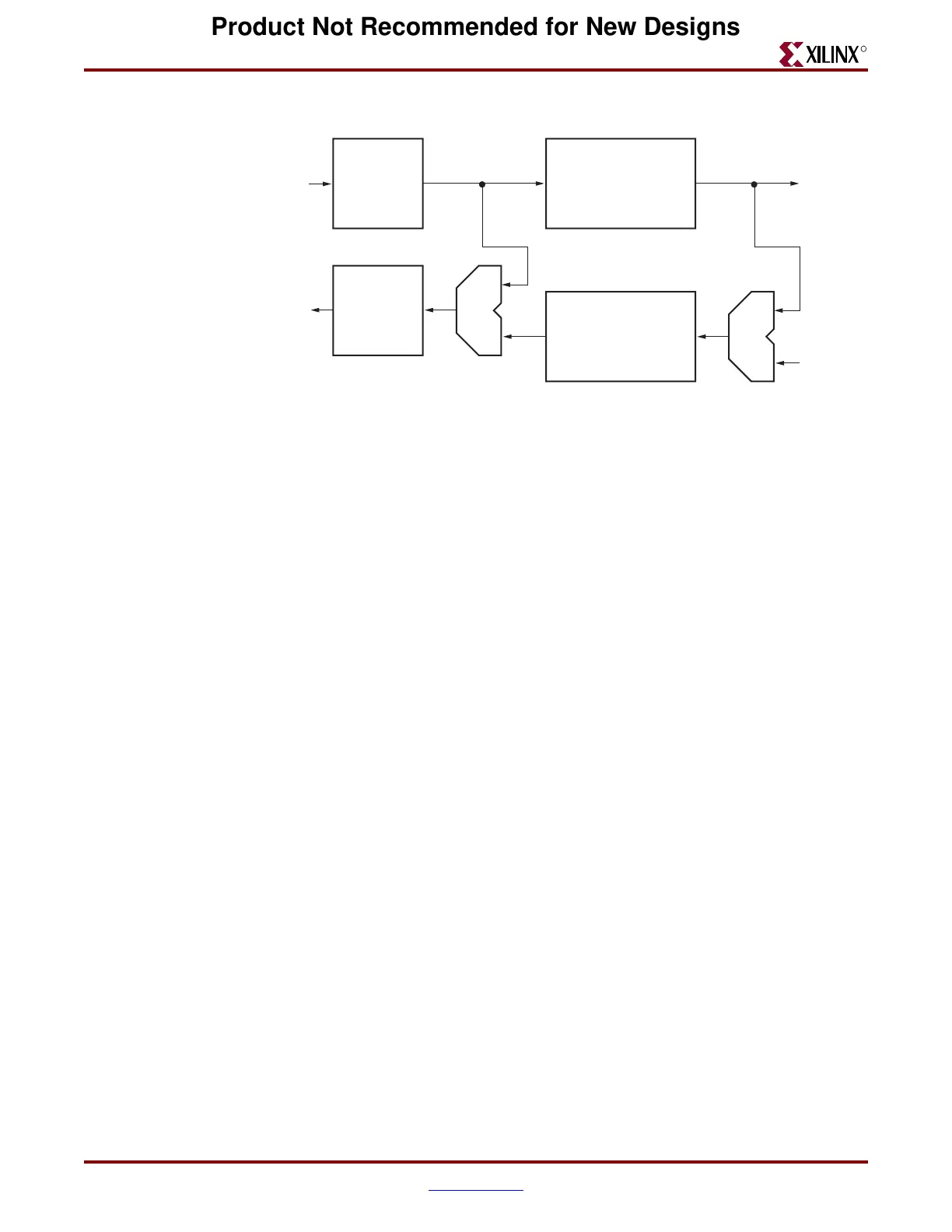

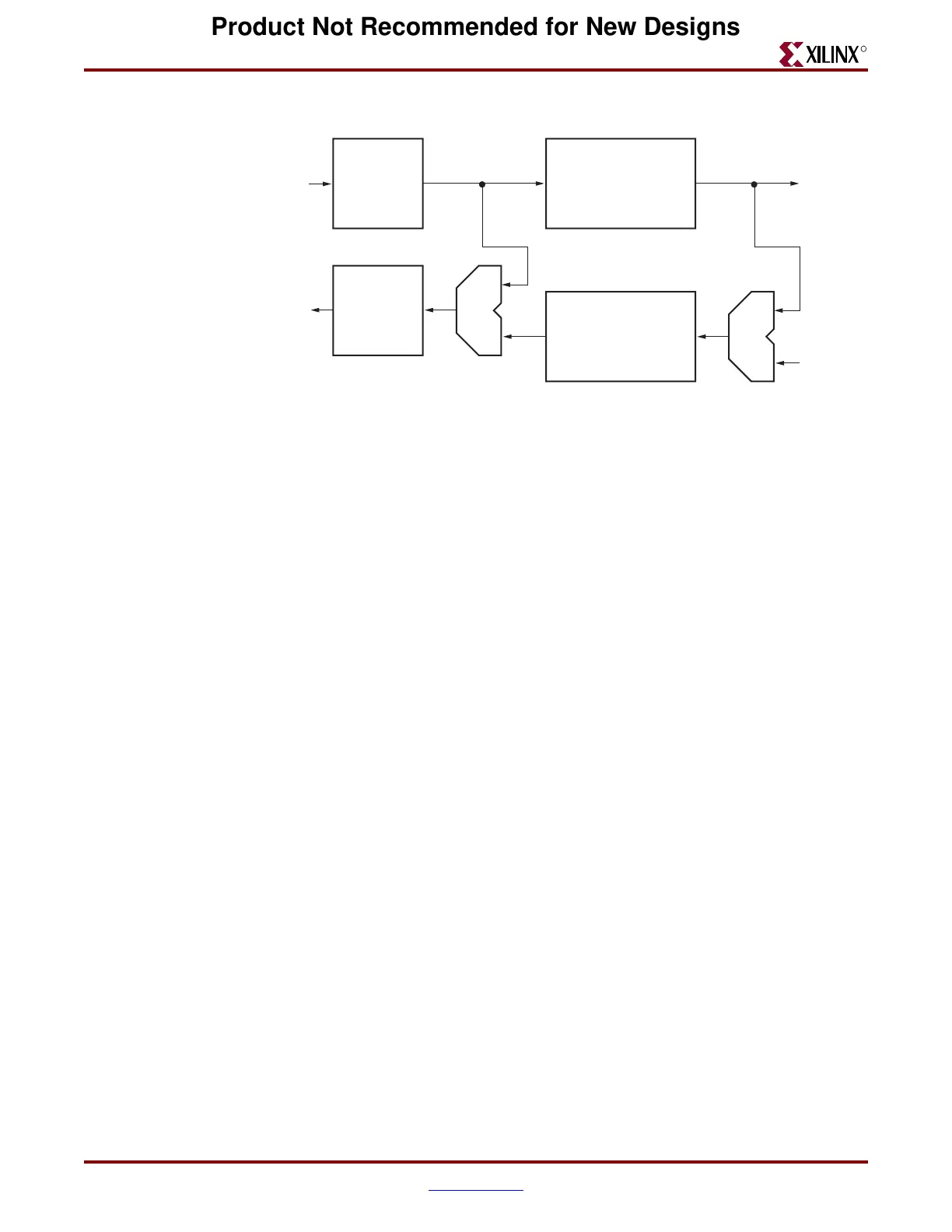

Figure 2-28: Serial and Parallel Loopback Logic

TXDATA

RXDATA

TXP/TXN

RXP/RXN

TX PCS TX SERIALIZER

RX DESERIALIZER

RX PCS MUX

MUX

PARALLEL

LOOPBACK = 01

SERIAL

LOOPBACK = 10

UG024_25_110503

Product Not Recommended for New Designs

Loading...

Loading...