50 www.xilinx.com RocketIO™ Transceiver User Guide

UG024 (v3.0) February 22, 2007

Chapter 2: Digital Design Considerations

R

.CLK180 ( ),

.CLK270 ( ),

.CLK2X ( ),

.CLK2X180 ( ),

.CLKDV ( clkdv2 ),

.CLKFX ( ),

.CLKFX180 ( ),

.LOCKED ( DCM_LOCKED ),

.PSDONE ( ),

.STATUS ( )

);

BUFG buf1 (

.I ( clkdv2 ),

.O ( USRCLK2_M )

);

BUFG buf2 (

.I ( clk_i ),

.O ( USRCLK_M )

);

IBUFG buf3(

.I ( REFCLKIN ),

.O ( REFCLKINBUF )

);

endmodule

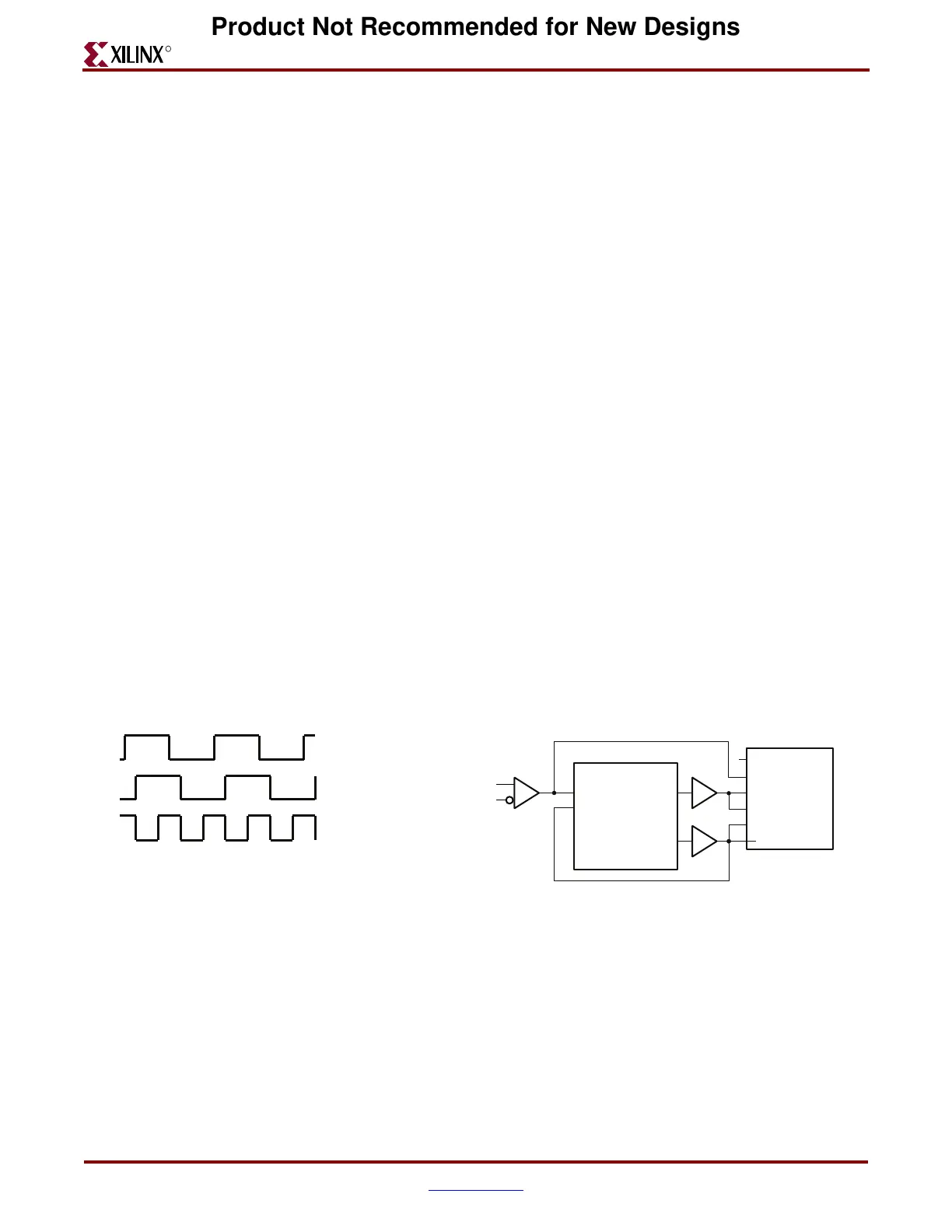

Example 3: One-Byte Clock

This is the 1-byte data path width clocking scheme example. USRCLK2_M is twice as fast

as USRCLK_M. It is also phase-shifted 180° for falling edge alignment.

VHDL Template

-- Module: ONE_BYTE_CLK

-- Description: VHDL submodule

-- DCM for 1-byte GT

--

-- Device: Virtex-II Pro Family

---------------------------------------------------------------------

library IEEE;

use IEEE.std_logic_1164.all;

Figure 2-5: One-Byte Clock

MGT + DCM for 1-Byte Data Path

GT_std_1

REFCLKSEL

REFCLK

TXUSRCLK2

RXUSRCLK2

TXUSRCLK

RXUSRCLK

CLKIN

CLKFB

RST

DCM

CLK2X180

CLK0

0

BUFG

BUFG

Clocks for 1-Byte Data Path

TXUSRCLK

RXUSRCLK

TXUSRCLK2

RXUSRCLK2

REFCLK

UG024_04_112202

REFCLK_P

IBUFGDS

REFCLK_N

Product Not Recommended for New Designs

Loading...

Loading...