54 www.xilinx.com RocketIO™ Transceiver User Guide

UG024 (v3.0) February 22, 2007

Chapter 2: Digital Design Considerations

R

Half-Rate Clocking Scheme

Some applications require serial speeds between 600 Mb/s and 1 Gb/s. (Refer to XAPP572

when considering running in this serial range.) The transceiver attribute SERDES_10B,

which sets the REFCLK multiplier to 10 instead of 20, enables the half-rate speed range

when set to TRUE. With this configuration, the clocking scheme also changes. The figures

below illustrate the three clocking scheme waveforms when SERDES_10B = TRUE.

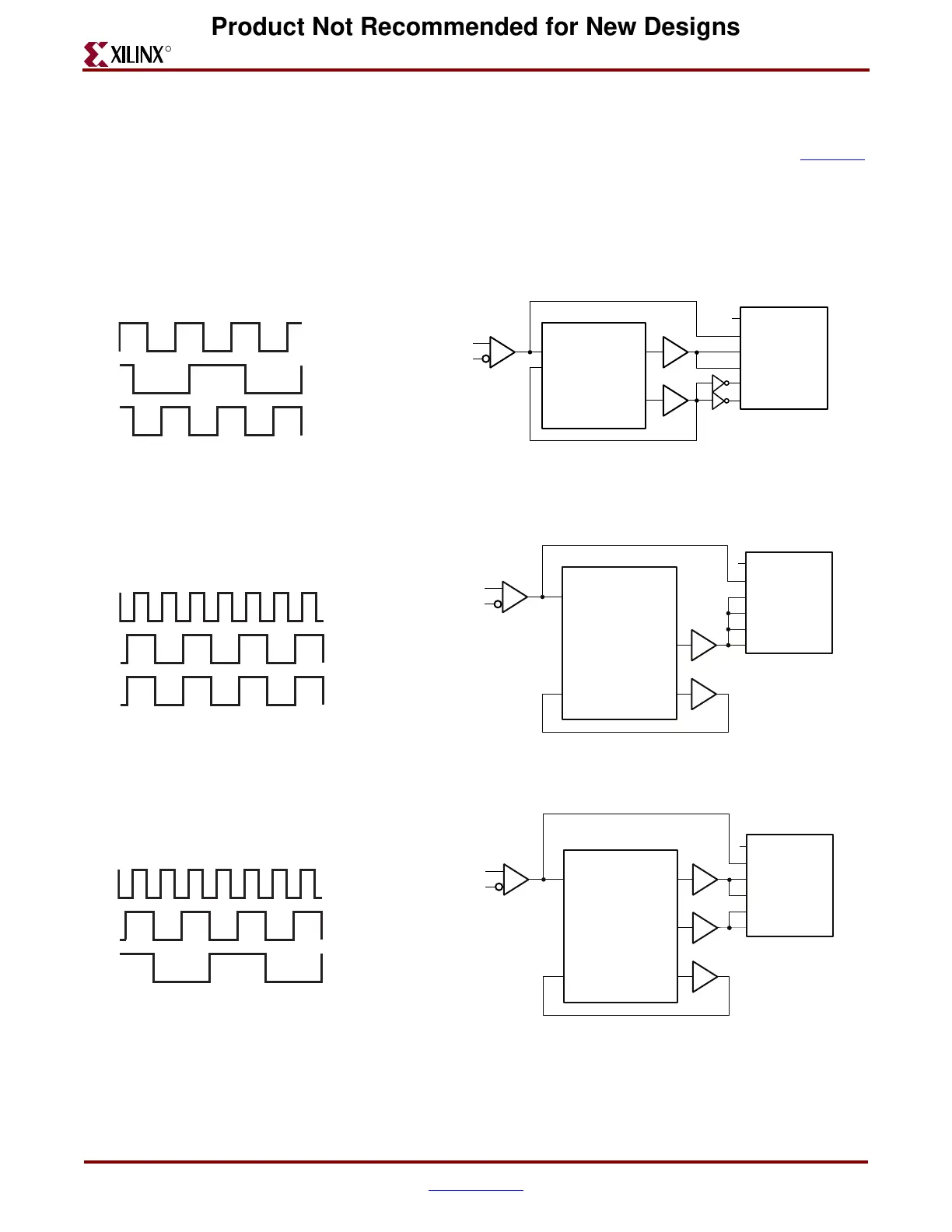

Figure 2-6: One-Byte Data Path Clocks, SERDES_10B = TRUE

Clocks for 1-Byte Data Path

(SERDES_10B = TRUE)

TXUSRCLK

RXUSRCLK

TXUSRCLK2

RXUSRCLK2

REFCLK

UG024_29_013103

CLKDV

CLKDV = divide by 2

MGT clock input invert-

ers (acceptable skew)

GT_std_1

REFCLKSEL

REFCLK

TXUSRCLK

RXUSRCLK

TXUSRCLK2

RXUSRCLK2

CLKIN

CLKFB

RST

DCM

CLK0

0

BUFG

BUFG

REFCLK_P

IBUFGDS

REFCLK_N

Figure 2-7: Two-Byte Data Path Clocks, SERDES_10B = TRUE

Clocks for 2-Byte Data Path

(SERDES_10B = TRUE)

TXUSRCLK

RXUSRCLK

TXUSRCLK2

RXUSRCLK2

REFCLK

UG024_30_013103

GT_std_2

REFCLKSEL

REFCLK

TXUSRCLK

RXUSRCLK

TXUSRCLK2

RXUSRCLK2

CLKIN

CLKFB

DCM

CLK0

CLKDV

0

BUFG

BUFG

REFCLK_P

IBUFGDS

REFCLK_N

CLKDV = divide by 2

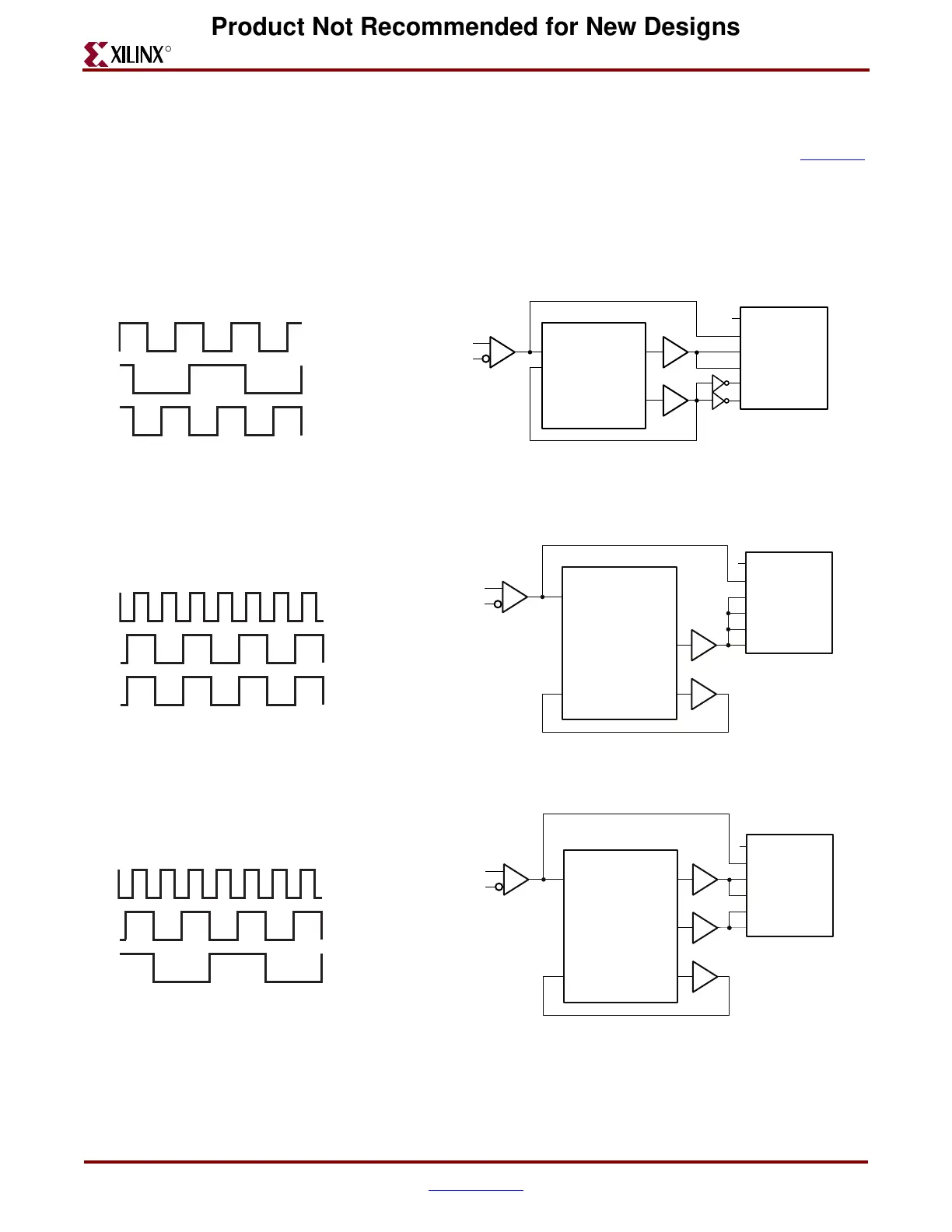

Figure 2-8: Four-Byte Data Path Clocks, SERDES_10B = TRUE

Clocks for 4-Byte Data Path

(SERDES_10B = TRUE)

TXUSRCLK

RXUSRCLK

TXUSRCLK2

RXUSRCLK2

REFCLK

UG024_31_013103

GT_std_4

REFCLKSEL

REFCLK

TXUSRCLK

RXUSRCLK

TXUSRCLK2

RXUSRCLK2

CLKIN

CLKFB

DCM

CLK_FX180

CLK0

CLKDV

0

BUFG

BUFG

BUFG

REFCLK_P

IBUFGDS

REFCLK_N

CLKDV = divide by 4

CLK_FX = divide by 2

Product Not Recommended for New Designs

Loading...

Loading...