40 www.xilinx.com RocketIO™ Transceiver User Guide

UG024 (v3.0) February 22, 2007

Chapter 2: Digital Design Considerations

R

±100 ppm or better, with jitter as low as possible. Module 3 of the Virtex-II Pro data sheet gives

further details.

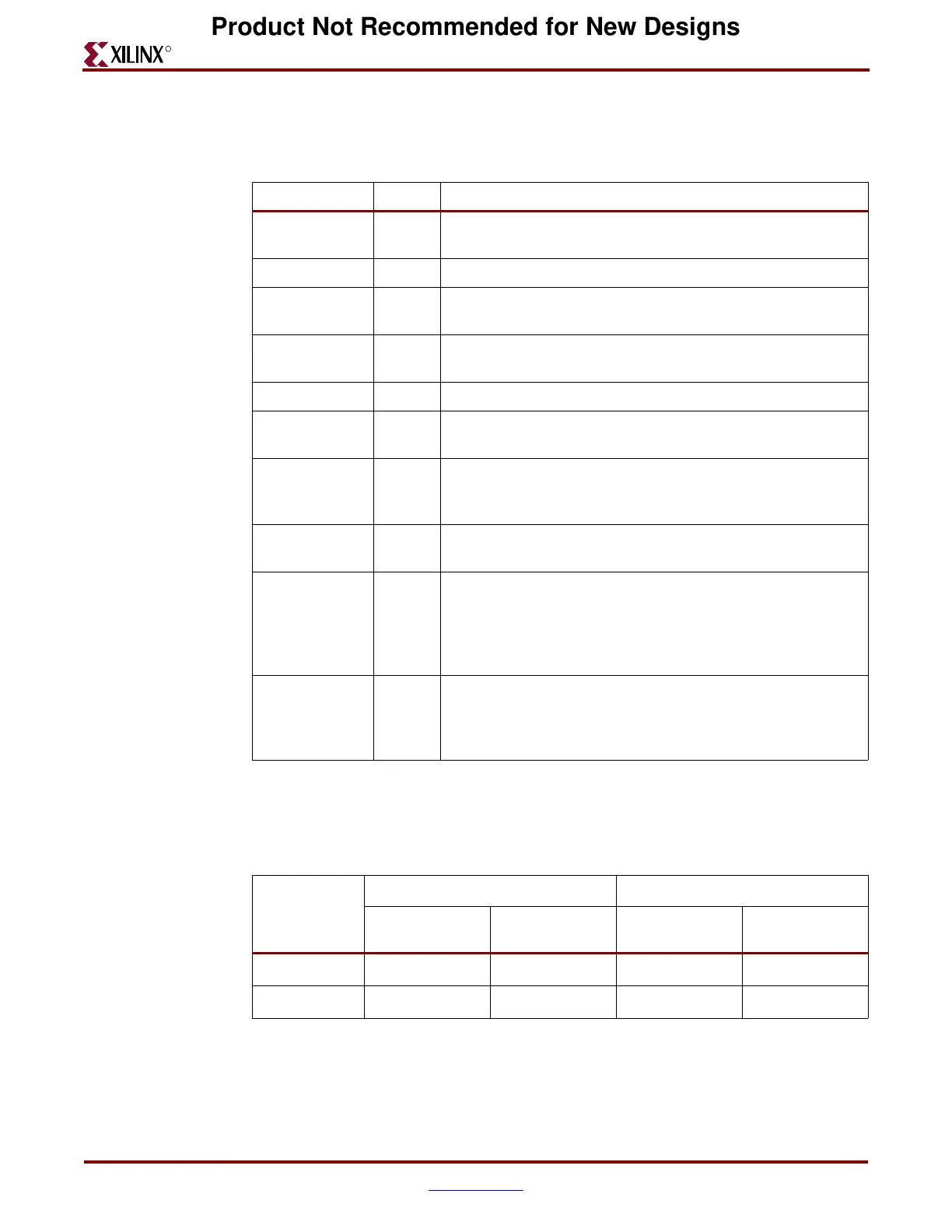

Table 2-1: Clock Ports

Clock I/Os Description

BREFCLK Input Reference clock used to read the TX FIFO and multiplied by

20 for parallel-to-serial conversion (20X)

BREFCLK2 Input Alternative to BREFCLK

RXRECCLK Output Recovered clock (from serial data stream) divided by 20.

Clocks data into the elastic buffer.

REFCLK Input Reference clock used to read the TX FIFO and multiplied by

20 for parallel-to-serial conversion (20X)

REFCLK2 Input Alternative to REFCLK.

REFCLKSEL Input Selects which reference clock is used. 0 selects REFCLK;

1 selects REFCLK2.

RXUSRCLK Input Clock from FPGA used for reading the RX Elastic Buffer.

Clock signals CHBONDI and CHBONDO into and out of the

transceiver. This clock is typically the same as TXUSRCLK.

TXUSRCLK

(1)

Input Clock from FPGA used for writing the TX Buffer. This clock

must be frequency locked to REFCLK for proper operation.

RXUSRCLK2 Input Clock from FPGA used to clock RX data and status between

the transceiver and FPGA fabric. The relationship between

RXUSRCLK2 and RXUSRCLK depends on the width of the

receiver data path. RXUSRCLK2 is typically the same as

TXUSRCLK2.

TXUSRCLK2

(1)

Input Clock from FPGA used to clock TX data and status between

the transceiver and FPGA fabric. The relationship between

TXUSRCLK2 and TXUSRCLK depends on the width of the

transmission data path.

Notes:

1. TXUSRCLK and TXUSRCLK2 must be driven by clock sources, even if only the receiver of the MGT is

being used.

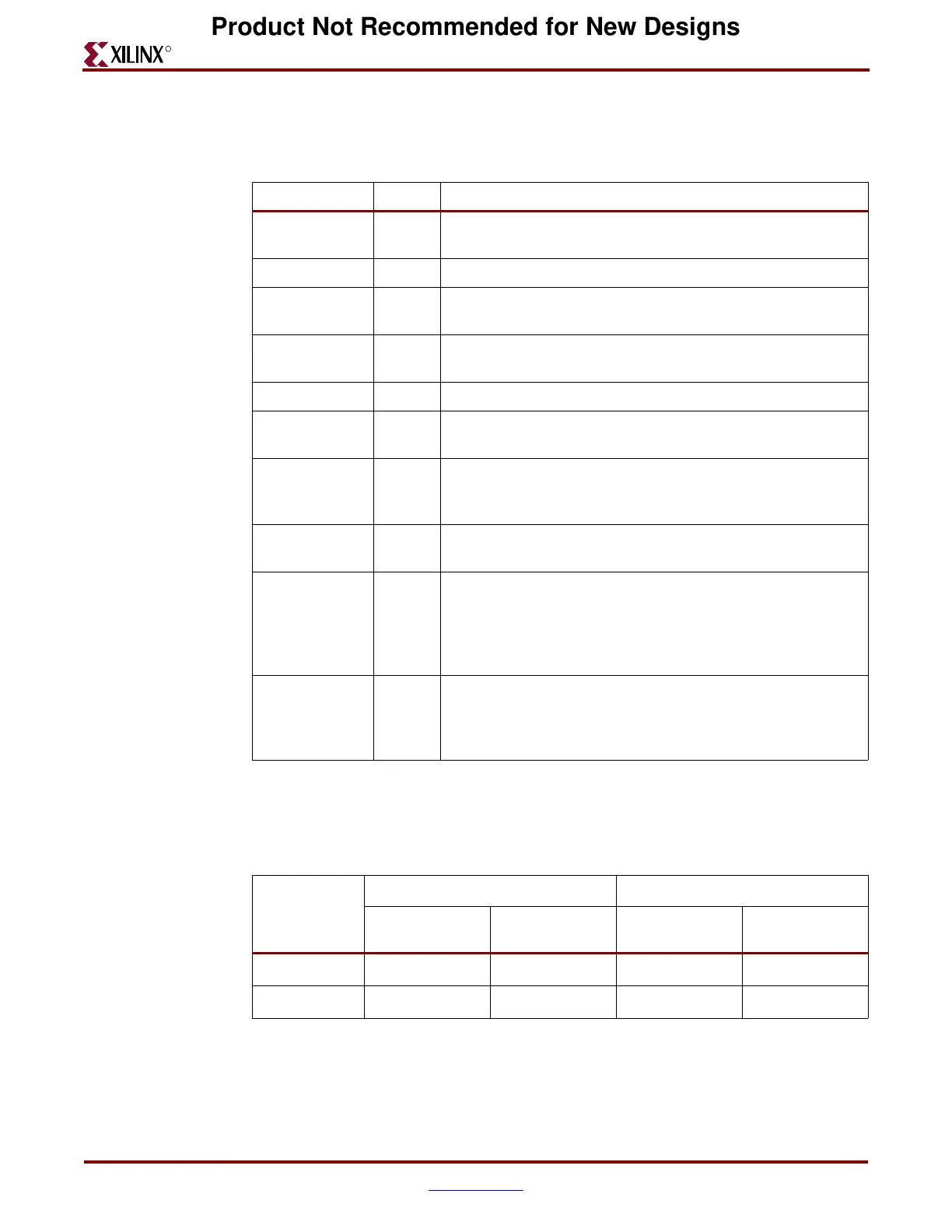

Table 2-2: Reference Clock Usage

Data Rate Routing

600 Mb/s –

2.499 Gb/s

2.500 Gb/s –

3.125 Gb/s

Can Route

Across Chip?

Can Route

Through BUFG?

REFCLK √√

(2)

√

(2)

BREFCLK √√

Note (1) Note (1)

Notes:

1. Because of dedicated routing to reduce jitter, BREFCLK cannot be routed through the fabric.

2. While this option is available in the silicon, this topography adds extra jitter to the reference clock

which can affect the overall performance of the transceiver.

Product Not Recommended for New Designs

Loading...

Loading...