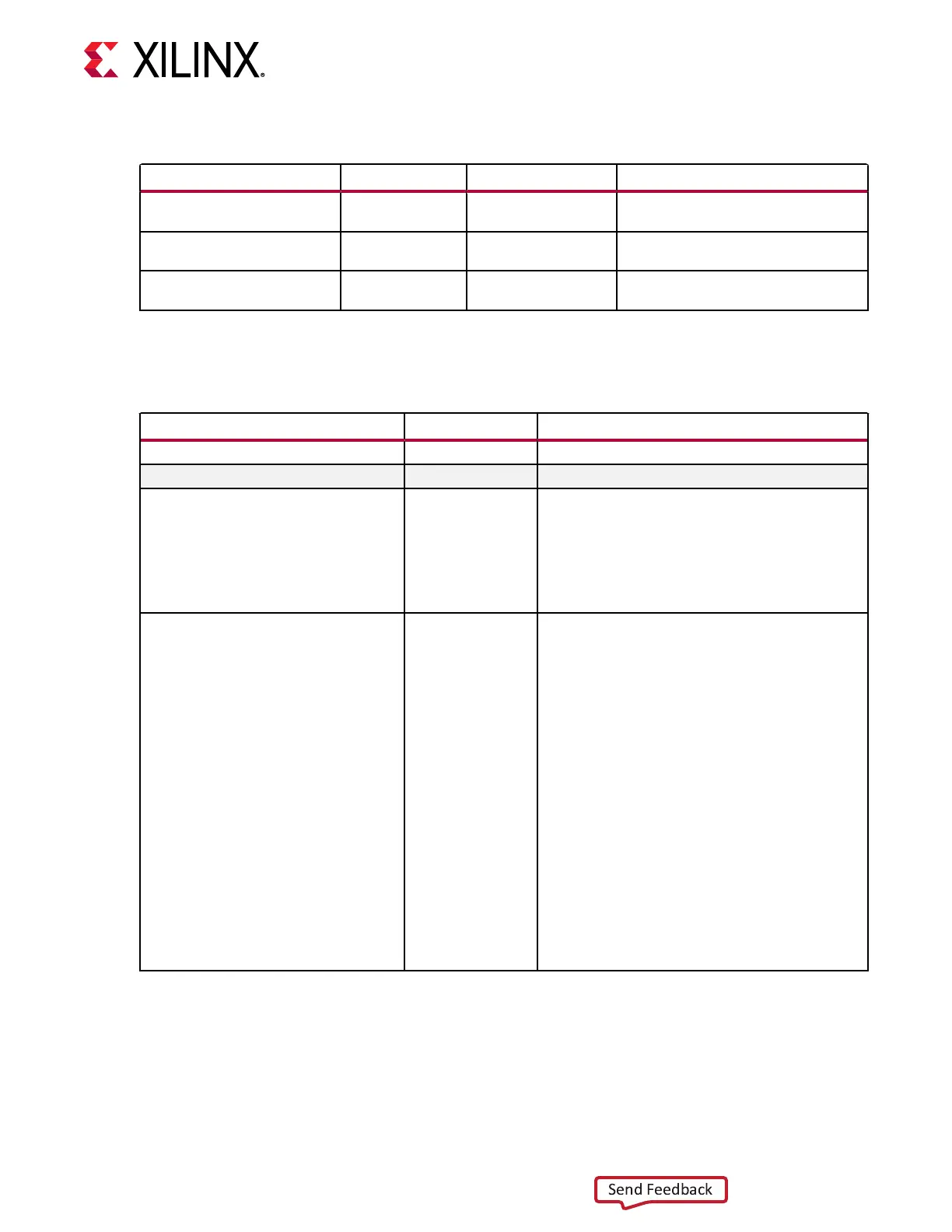

Table 48: RX AFE ports (cont'd)

Ports Dir Clock Domain Description

BGRCALOVRD[4:0] In Async Reserved. This port must be set to

5’b11111. Do not modify this value.

BGRCALOVRDENB In Async Reserved. This port must be set to 1’b1.

Do not modify this value.

RCALENB In Async Reserved. This port must be set to 1’b1.

Do not modify this value.

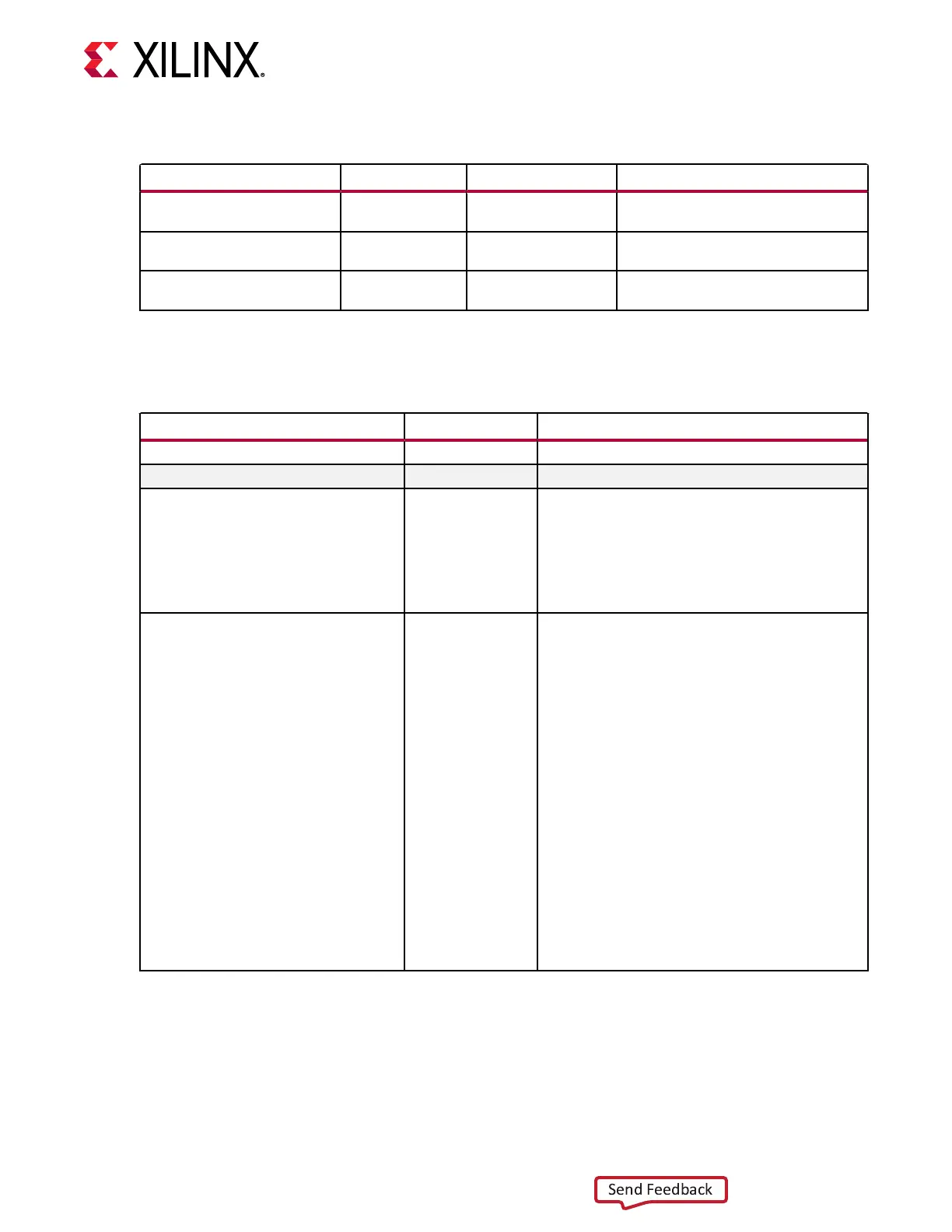

The following table denes the RX AFE aributes.

Table 49: RX AFE Attributes

Attribute Type Description

CH[0/1]_RX_PAD_CFG0 16-bit Reserved.

Bit Name Address Description

PAD_RTERM_VCOM_MODE [12:11] Controls the mode for the RX termination voltage:

2’b00: AVTT

2’b01: Reserved

2’b10: Floating

2’b11: Programmable

PAD_RTERM_VCOM_LVL

[10:7] Controls the common mode in programmable mode:

4’b0000: 100 mV

4’b0001: 200 mV

4’b0010: 250 mV

4’b0011: 300 mV

4’b0100: 350 mV

4’b0101: 400 mV

4’b0110: 500 mV

4’b0111: 550 mV

4’b1000: 600 mV

4’b1001: 700 mV

4’b1010: 800 mV

4’b1011: 850 mV

4’b1100: 900 mV

4’b1101: 950 mV

4’b1110: 1000 mV

4’b1111: 1100 mV

GTM Use Modes - RX Termination

This secon describes the GTM use modes with RX terminaon.

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 86

Loading...

Loading...