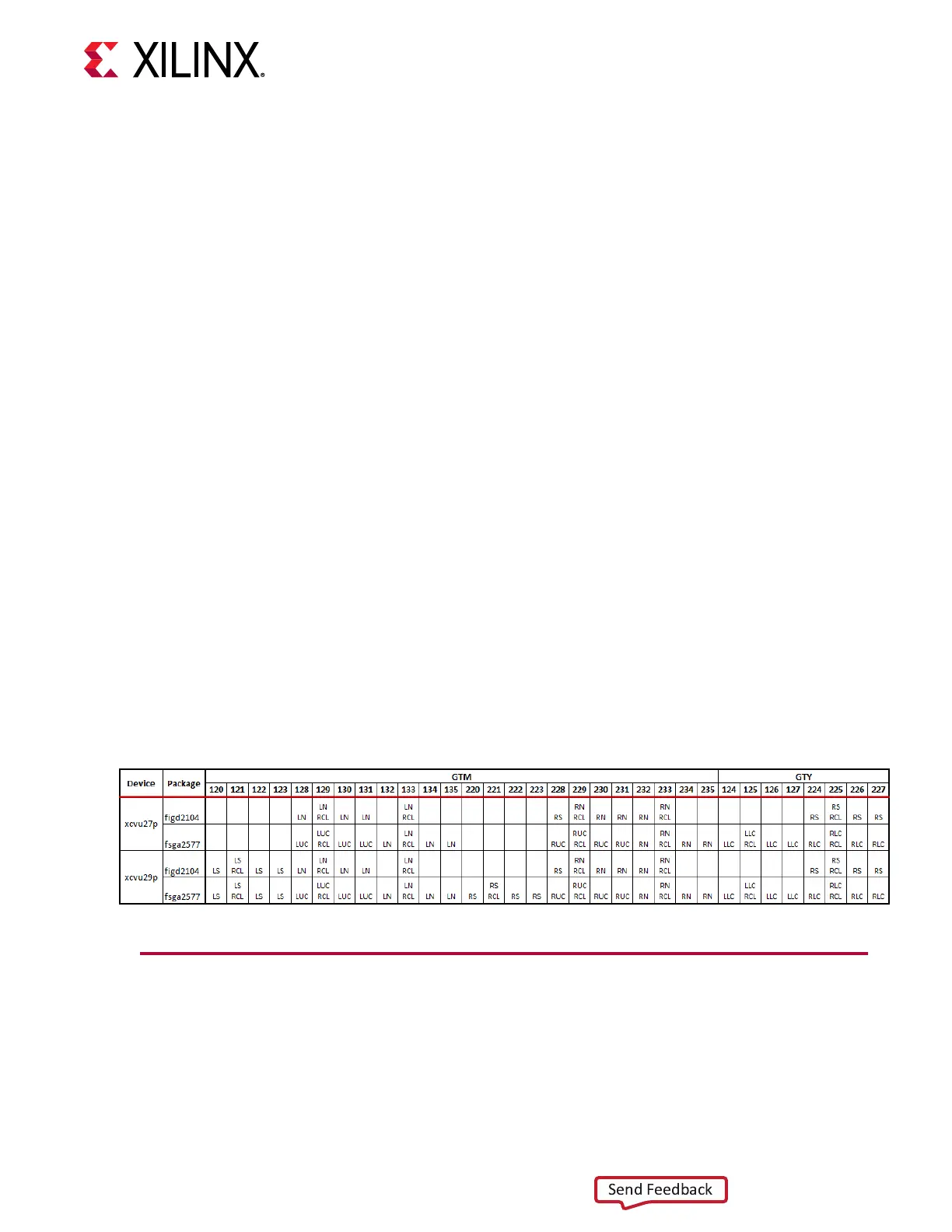

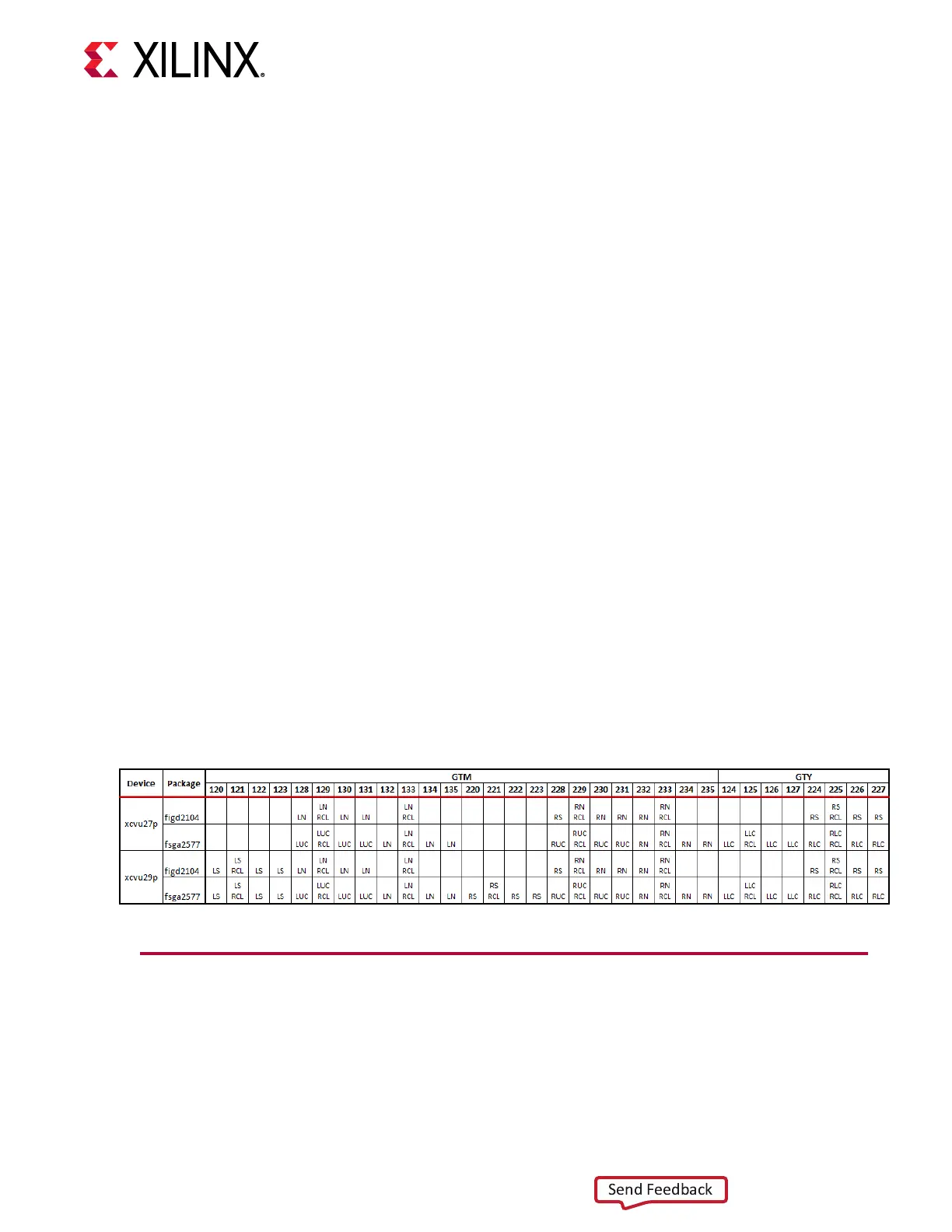

Analog Power Supply Pins

The GTM transceiver Dual power supplies (MGTAVCC, MGTAVTT, VCCINT_GT, and

MGTVCCAUX) have planes inside the package. For some of the packages, there are mulple

planes for each analog power supply. It there is more than one PSG in the package, the power

supply pin names have a sux (such as _LN, _RN, _LS, or _RS) that idenes which pins are

associated with which PSG. If all of the Duals in a PSG are not used, the associated power pins

can be le unconnected or ed to GND. The rules for powering PSGs are as follows:

• Within a package PSG, if no Duals are used, the PSG can be unpowered.

• If any Duals in a PSG are used, the PSG must be powered.

• PSGs on each side (le or right) of the package are fully independent. Powering or not

powering PSGs on one side of the package does not aect the PSGs on the other sides of the

package.

• If a PSG does not have an RCAL master and it is powered, all the PSGs on that side (le or

right) of the package must be powered.

• If a PSG with an RCAL master is unpowered, any PSGs without an RCAL master on that side

of the package must also be unpowered.

• A PSG that does not have an RCAL master can be unpowered without aecng other PSGs.

For each GTM transceiver power supply group there are four power supplies (MGTAVCC,

MGTAVTT, VCCINT_GT and MGTVCCAUX). For example, if there are two PSGs in a package,

then there are a total of six power supply planes in the package for these groups, with three

planes in the package for each PSG. The following table shows the PSGs for Virtex UltraScale+

devices.

Figure 48: UltraScale+ Device Transceiver Power Supply Groups and RCAL Master

Reference Clock

This secon focuses on the selecon of the reference clock source or oscillator. An oscillator is

characterized by:

• Frequency range

Chapter 5: Board Design Guidelines

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 120

Loading...

Loading...