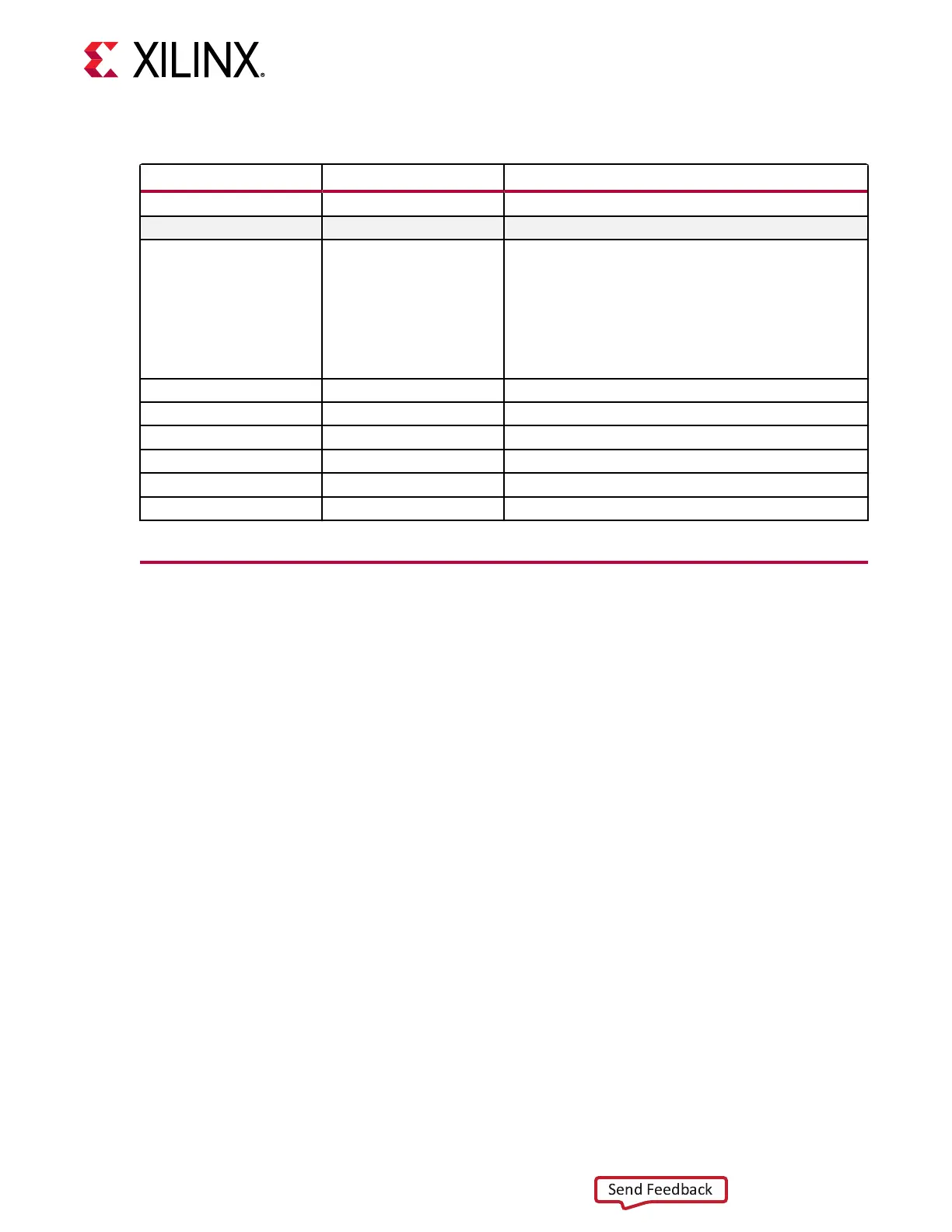

Table 10: LCPLL Attributes (cont'd)

Attributes Type Description

SDM_CFG0[15:0] 16-bit Reserved. Use the recommended value from the Wizard.

Bit Name Address Description

SDM_WIDTHSEL [10:9] This attribute sets the denominator of the fractional part of

the feedback divider:

2'b00: 24 bits.

2'b01: 20 bits.

2'b10: 16 bits.

2'b11: Reserved.

SDM_CFG1

16-bit Reserved. Use the recommended value from the Wizard.

SDM_CFG2 16-bit Reserved. Use the recommended value from the Wizard.

SDM_SEED_CFG0 16-bit Reserved. Use the recommended value from the Wizard.

SDM_SEED_CFG1 16-bit Reserved. Use the recommended value from the Wizard.

A_SDM_DATA_CFG0 16-bit Reserved. Use the recommended value from the Wizard.

A_SDM_DATA_CFG1 16-bit Reserved. Use the recommended value from the Wizard.

Reset and Initialization

The GTM transceiver must be inialized aer device power-up and conguraon before it can be

used. The GTM transmier (TX) and receiver (RX) can be inialized independently and in parallel

as shown in the following gure. The GTM transceiver TX and RX inializaon comprises three

steps:

1. Inializing the associated PLL driving TX/RX

2. Inializing the TX and RX datapaths (PMA + PCS)

The TX and RX in the GTM transceiver receive the clock through the LCPLL in the transceiver's

own Dual. In the power-on inializaon sequence, the LCPLL used by the TX and RX must be

inialized rst. The LCPLL used by the TX and RX is reset individually and its reset operaon

independent from TX and RX resets. The TX and RX datapaths must be inialized only aer the

associated LCPLL is locked.

Chapter 2: Shared Features

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 23

Loading...

Loading...