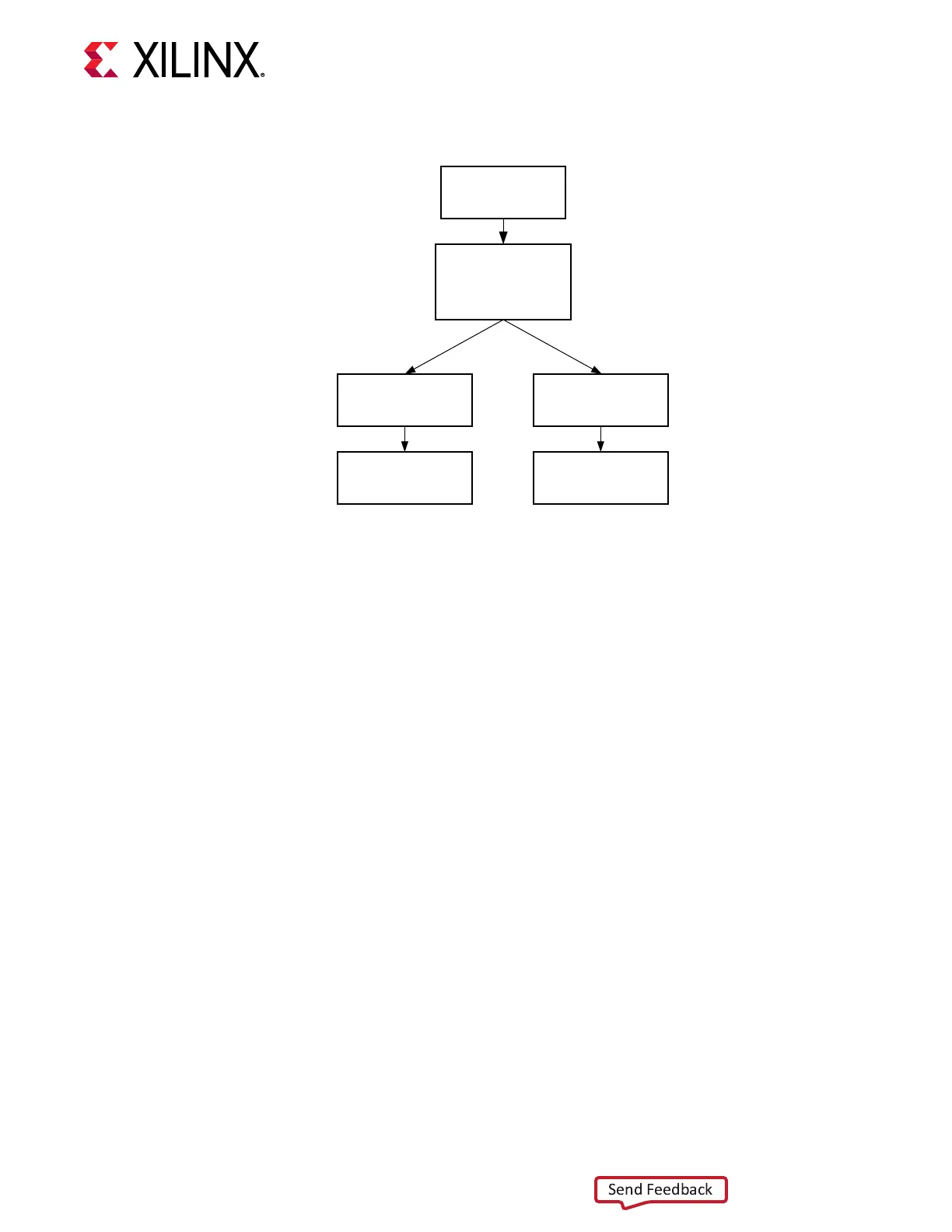

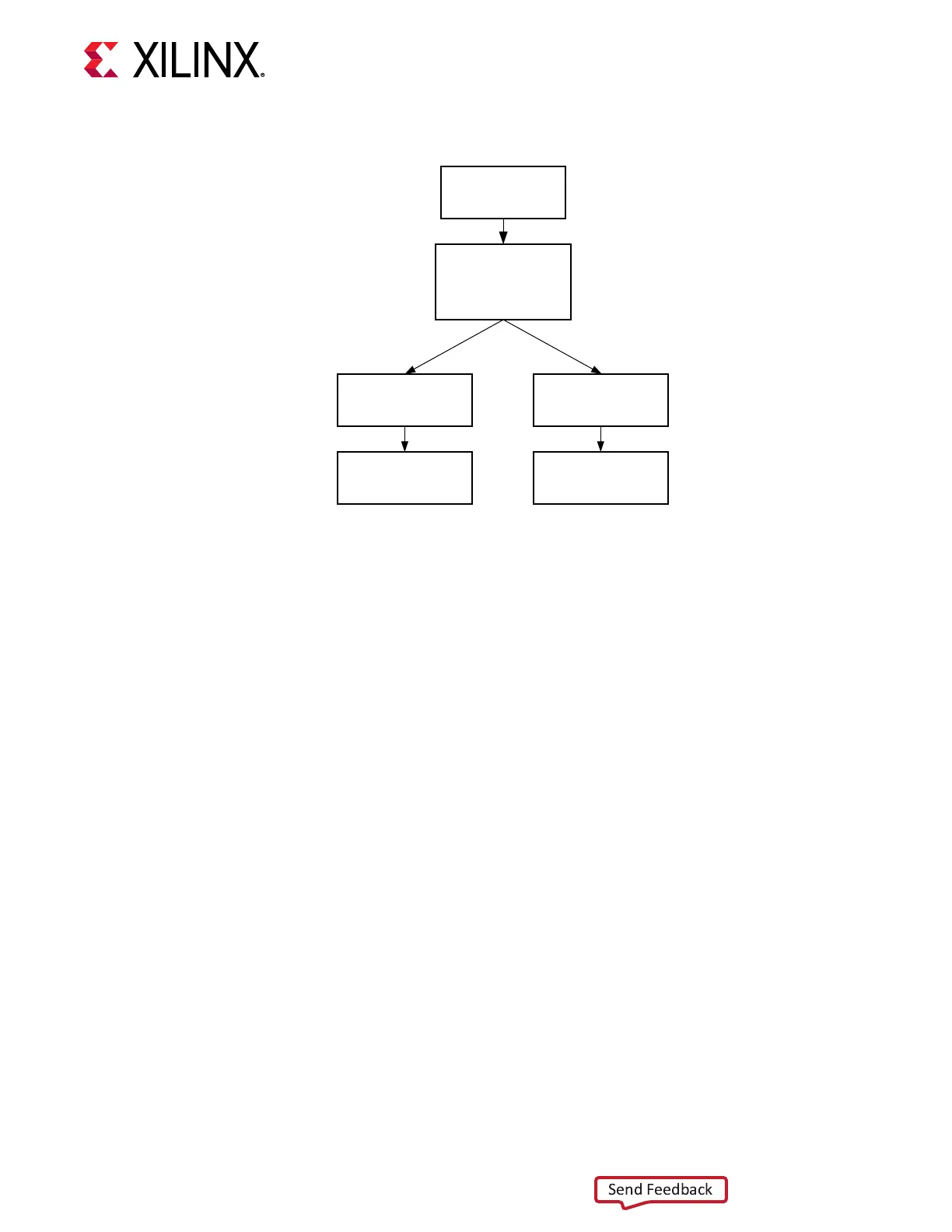

Figure 11: GTM Transceiver Initialization Overview

After Configuration

LCPLL Reset

TX Initialization by

GTTXRESET

RX Initialization by

GTRXRESET

RXRESETDONETXRESETDONE

X20903-052818

The GTM transceiver TX and RX use a state machine to control the inializaon process. They

are paroned into a few reset regions. The paron allows the reset state machine to control

the reset process in a sequence that the PMA can be reset rst and the PCS can be reset aer

the asseron of the TXUSERRDY or RXUSERRDY. It also allows the PMA, the PCS, and

funconal blocks inside them to be reset individually when needed during normal operaon.

The GTM transceiver oers two types of reset: inializaon and component.

• Inializaon Reset: This reset is used for complete GTM transceiver inializaon. It must be

used aer device power-up and conguraon. During normal operaon, when necessary,

GTTXRESET and GTRXRESET can also be used to reinialize the GTM transceiver TX and RX.

GTTXRESET is the inializaon reset port for the GTM transceiver TX. GTRXRESET is the

inializaon reset port for the GTM transceiver RX. During inializaon reset,

TXRESETMODE and RXRESETMODE should be set to sequenal mode. All TX PMA, TX PCS,

RX PMA, and RX PCS component resets should be enabled by seng all required component

bits of TXPMARESETMASK, TXPCSRESETMASK, RXPMARESETMASK, and

RXPCSRESETMASK to High.

• Component Reset: This reset is used for special cases and specic subsecon resets while the

GTM transceiver is in normal operaon. The component that is required to be reset is selected

by seng the associated bit within TXPMARESETMASK, TXPCSRESETMASK,

RXPMARESETMASK, or RXPCSRESETMASK to High. A TX component reset is triggered by

toggling the GTTXRESET port. An RX component reset is triggered by toggling the

GTRXRESET port. Separate component reset ports are available. For the TX, these are

TXCKALRESET, TXFECRESET, TXPCSRESET, and TXPMARESET. For the RX, these are

RXADAPTRESET, RXADCCLKGENRESET, RXBUFRESET, RXCDRFRRESET, RXCDRPHRESET,

RXDFERESET, RXDSPRESET, RXEYESCANRESET, RXFECRESET, RXPCSRESET,

RXPMARESET, and RXPRBSCSCNTRST.

Chapter 2: Shared Features

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 24

Loading...

Loading...