TX Interface

The TX interface is the gateway to the TX datapath of the GTM transceiver. Applicaons

transmit data through the GTM transceiver by wring data to the TXDATA port on the posive

edge of TXUSRCLK2. Port widths can be 64 and 128 bits for NRZ mode, or 80, 128, 160, and

256 bits for PAM4 mode. The rate of the parallel clock (TXUSRCLK2) at the interface is

determined by the TX line rate and the width of the TXDATA port. A second parallel clock

(TXUSRCLK) must be provided for the internal PCS logic in the transmier. This secon shows

how to drive the parallel clocks and explains the constraints on those clocks for correct

operaon.

Interface Width Configuration

The GTM transceiver contains a 64-bit internal datapath in NRZ mode and an 80-bit and 128-bit

internal datapath in PAM4 mode that is congurable by seng the TX_INT_DATA_WIDTH

aribute. When the FEC is enabled, only the 80-bit internal datapath may be used. The interface

width is congurable by seng the TX_DATA_WIDTH aribute. In NRZ mode,

TX_DATA_WIDTH can be congured to 64 or 128 bits. In PAM4 mode, TX_DATA_WIDTH can

be congured to 80, 128, 160, or 256 bits. When the FEC is enabled, only the 80-bit or 160-bit

data width can be selected.

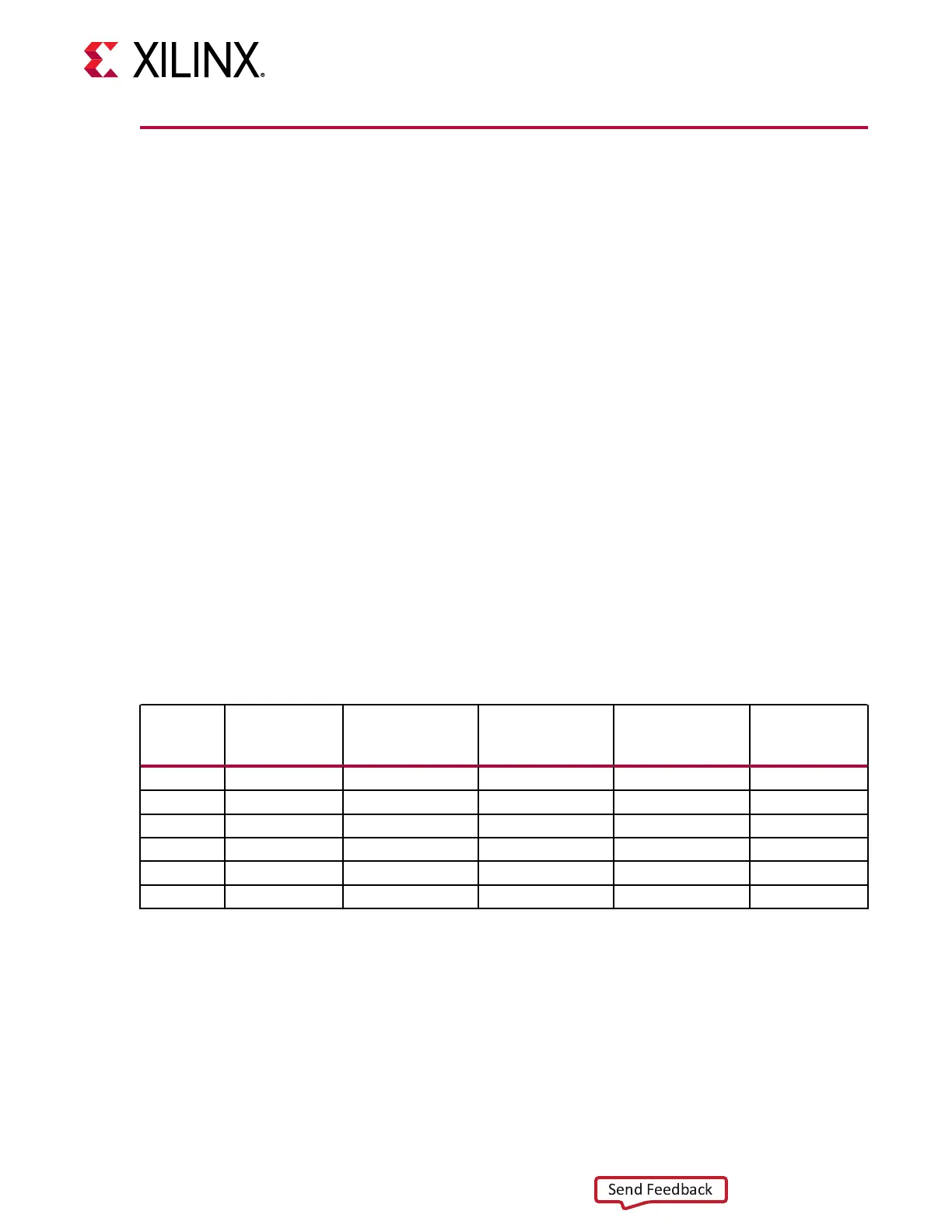

The following table shows how the interface width for the TX datapath is selected.

Table 28: TX Interface Datapath Configuration

Encoding FEC Allowed?

TX_DATA_WIDTH

Encoding

TX Data Width

Selection

TX_INT_DATA_WI

DTH Encoding

TX Internal

Datapath

Selection

NRZ No 0 64 0 64

NRZ No 2 128 0 64

PAM4 Yes 1 80 1 80

PAM4 Yes 3 160 1 80

PAM4 No 2 128 2 128

PAM4 No 4 256 2 128

The following gure shows how the TX data is transmied.

Chapter 3: Transmitter

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 55

Loading...

Loading...