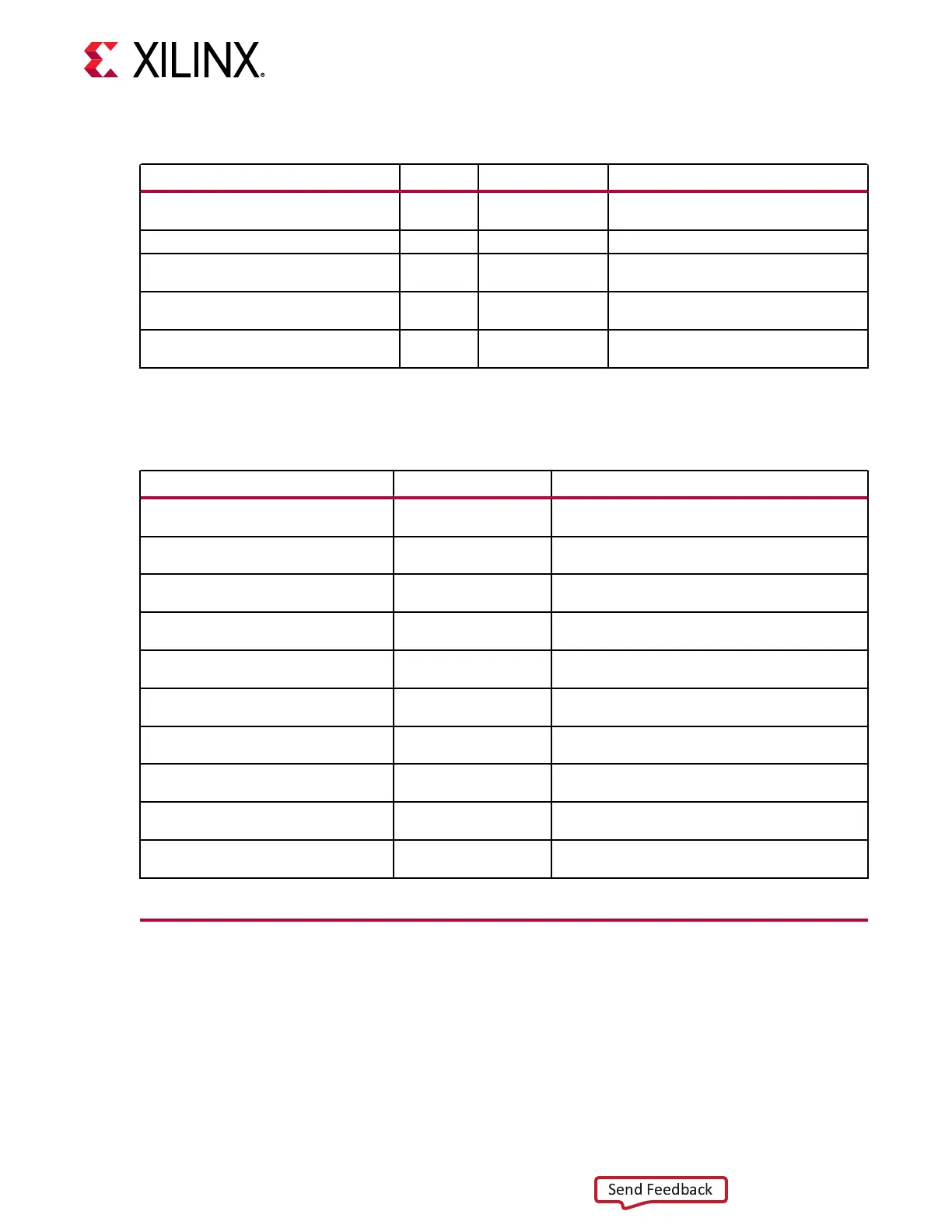

Table 52: CDR Ports (cont'd)

Port Dir Clock Domain Description

CH[0/1]_RXCDRFRRESET In Async Reserved. Use the recommended value

from the Wizard.

CH[0/1]_RXCDRHOLD In Async Hold the CDR control loop frozen.

CH[0/1]_RXCDRINCPCTRL In Async Reserved. Use the recommended value

from the Wizard.

CH[0/1]_RXCDRPHRESET In Async Reserved. Use the recommended value

from the Wizard.

CH[0/1]_RXCDRFREQOS In Async Reserved. Use the recommended value

from the Wizard.

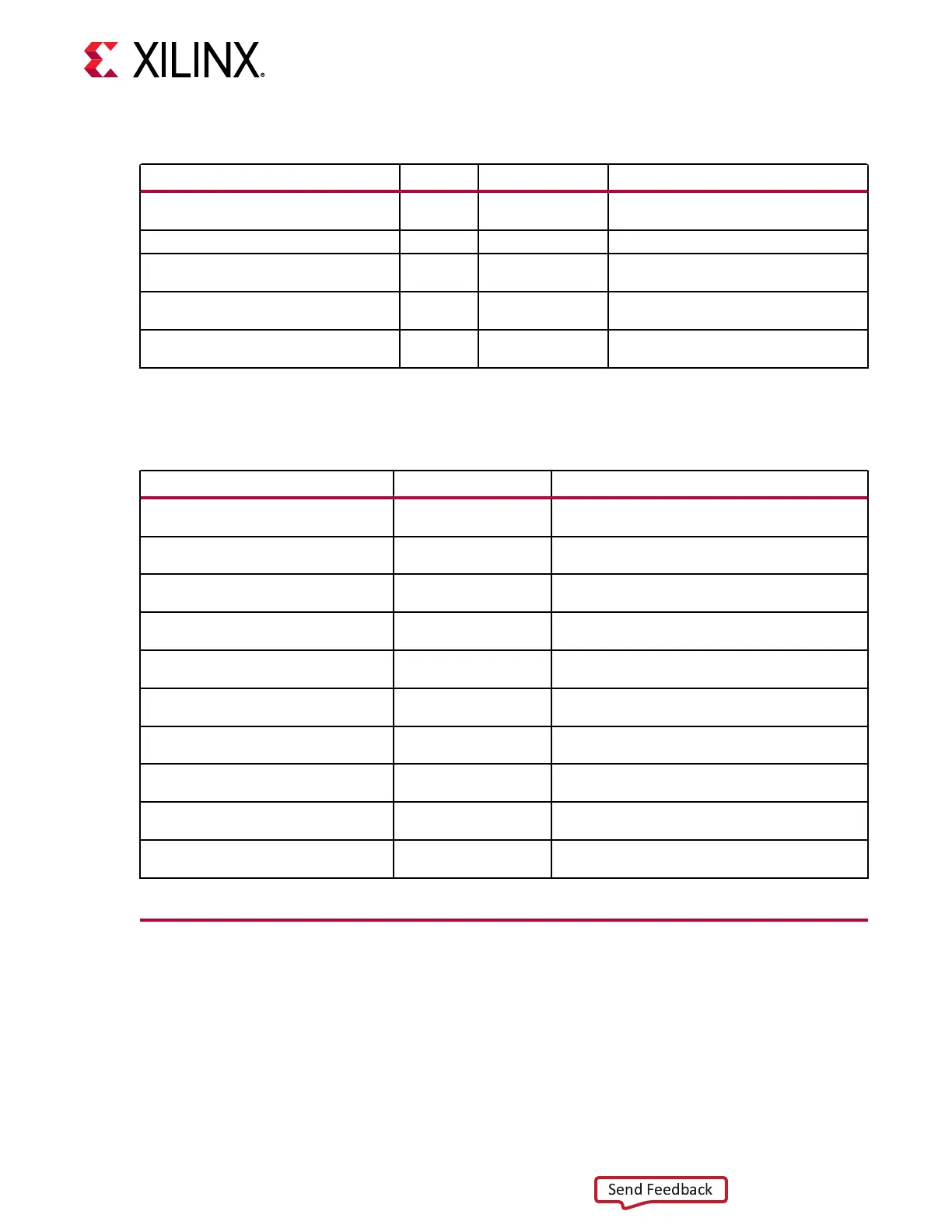

The following table denes the CDR aributes.

Table 53: CDR Attributes

Attribute Type Description

CH[0/1]_RX_CDR_CFG0A 16-bit CDR configuration. Use the recommended value

from the Wizard.

CH[0/1]_RX_CDR_CFG0B 16-bit CDR configuration. Use the recommended value

from the Wizard.

CH[0/1]_RX_CDR_CFG1A 16-bit CDR configuration. Use the recommended value

from the Wizard.

CH[0/1]_RX_CDR_CFG1B 16-bit CDR configuration. Use the recommended value

from the Wizard.

CH[0/1]_RX_CDR_CFG2A 16-bit CDR configuration. Use the recommended value

from the Wizard.

CH[0/1]_RX_CDR_CFG2B 16-bit CDR configuration. Use the recommended value

from the Wizard.

CH[0/1]_RX_CDR_CFG3A 16-bit CDR configuration. Use the recommended value

from the Wizard.

CH[0/1]_RX_CDR_CFG3B 16-bit CDR configuration. Use the recommended value

from the Wizard.

CH[0/1]_RX_CDR_CFG4A 16-bit CDR configuration. Use the recommended value

from the Wizard.

CH[0/1]_RX_CDR_CFG4B 16-bit CDR configuration. Use the recommended value

from the Wizard.

RX Fabric Clock Output Control

The RX Clock Divider Control block has two main components: serial clock divider control, and

parallel clock divider and selector control. The clock divider and selector details are illustrated in

the following gure.

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 94

Loading...

Loading...