Chapter 3. Product information 85

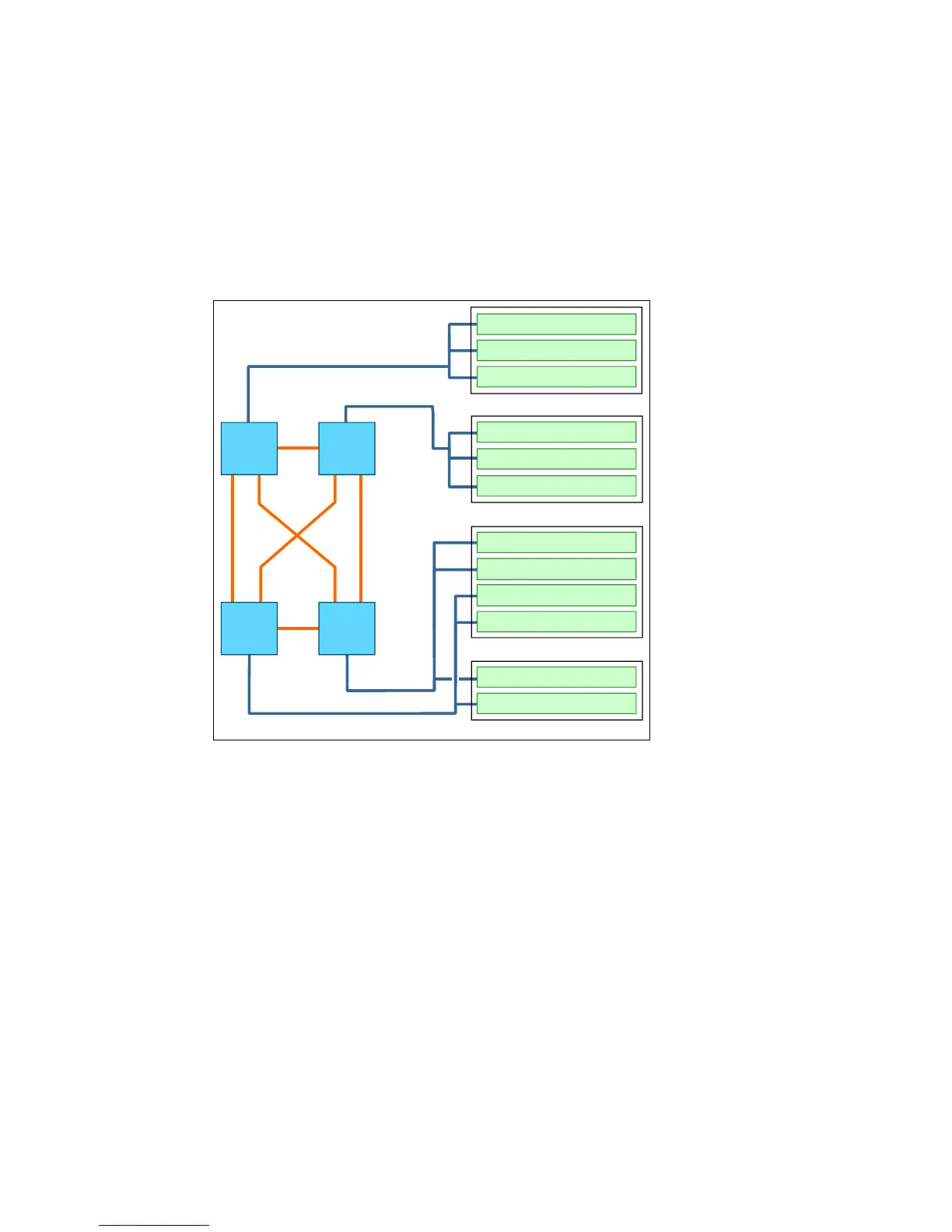

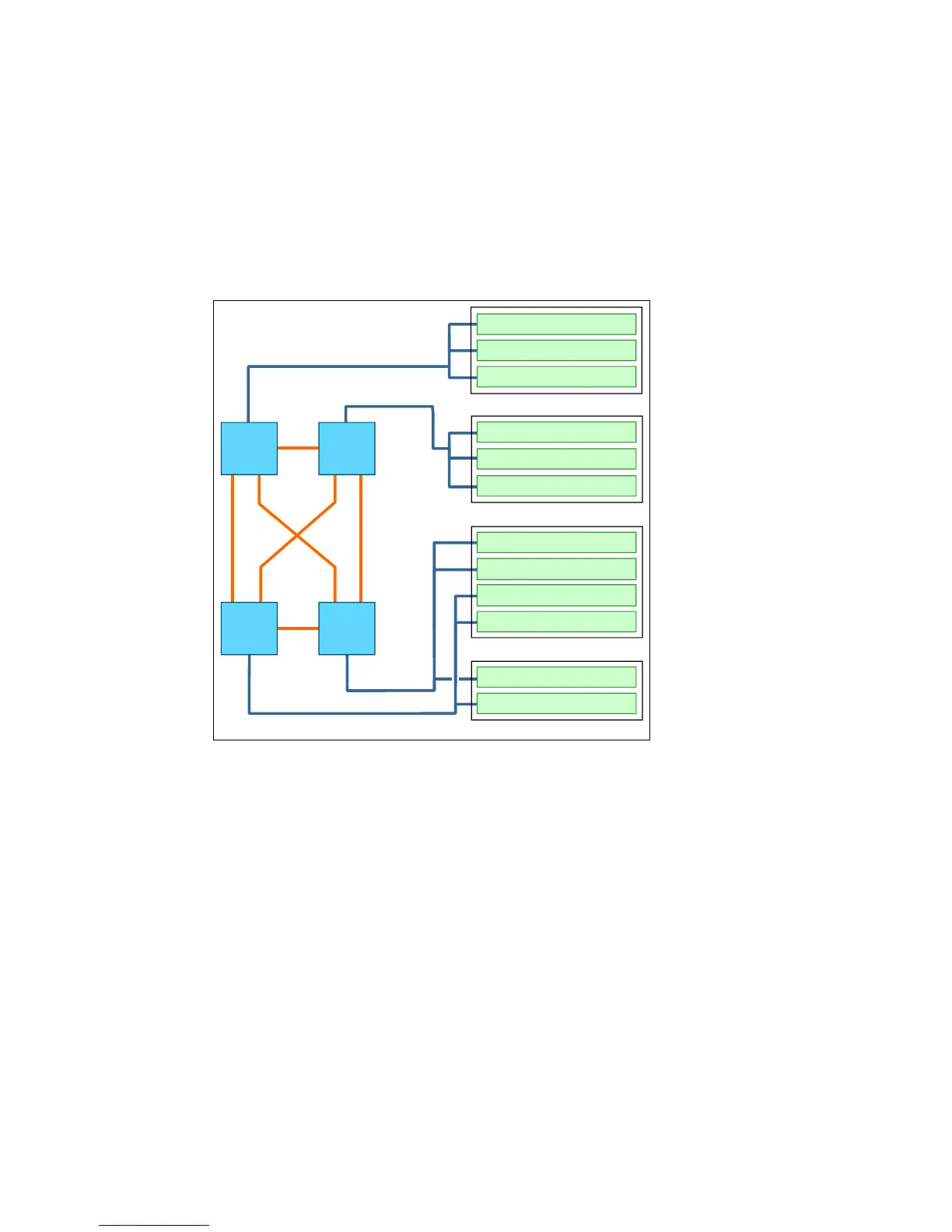

The PCIe lanes used in the I/O Books and Storage Book are connected to installed

processors as follows:

The slots in the Primary I/O Book and Storage I/O Book connect either to processor 1 or

processor 2.

The slots in the Optional I/O Book in bay 1 connect to processor 4.

The slots in the Optional I/O Book in bay 2 connect to processor 3.

This PCIe connectivity is shown in Figure 3-23.

Figure 3-23 Block diagram of the PCIe connectivity in the x3850 X6

3.12 Primary I/O Book

The Primary I/O Book is the core module, which provides base I/O connectivity, with four

PCIe slots:

Two PCIe 3.0 x16 slots (x16-wired), half-length, full-height, up to 75W of power

One PCIe 3.0 x16 (x8-wired), half-length, full-height, up to 75W of power

One Mezzanine LOM Generation 2 (ML2) slot for network adapters with the new ML2 form

factor (PCIe 3.0 x8)

As shown in Figure 3-23, the use of all slots in the Primary I/O Book requires two processors

(two Compute Books) installed:

Processor 1 drives a PCIe x16 slot and the ML2 slot

Processor 2 drives the other PCIe 16 slot and the PCI x8 slot

QPI links

Intel

Xeon

CPU 1

Slot 7: PCIe 3.0 x16 (x16)

Slot 9: PCIe 3.0 x16 (x16)

Slot 10: Mezz LOM (x8)

Slot 12: PCIe 3.0 x16 (x8)

Intel

Xeon

CPU 2

Slot 8: PCIe 3.0 x16 (x8)

Slot 11: PCIe 3.0 x16 (x8)

Intel

Xeon

CPU 4

Intel

Xeon

CPU 3

Slot 1

Slot 2

Slot 3

Slot 4

Slot 5

Slot 6

Storage Book

Primary I/O Book

Optional I/O Book in Bay 2

Optional I/O Book in Bay 1

PCIe 3.0 lanes

Loading...

Loading...