177

Sequence Input Instructions Section 3-3

3-3-9 Differentiated and Immediate Refreshing Instructions

The LOAD, AND, and OR instructions have differentiated and immediate

refreshing variations in addition to their ordinary forms, and there are also two

combinations available.

The LOAD NOT, AND NOT, OR NOT, OUT, and OUT NOT instructions have

immediate refreshing variations in addition to their ordinary forms.

The I/O timing for data handled by instructions differs for ordinary and differ-

entiated instructions, immediate refreshing instructions, and immediate

refreshing differentiated instructions.

Ordinary and differentiated instructions are executed using data input by pre-

vious I/O refresh processing, and the results are output with the next I/O pro-

cessing. Here “I/O refreshing” means the data exchanged between the CPU’s

internal memory and the I/O Unit.

In addition to the above I/O refreshing, an immediate refresh instruction

exchanges data with the I/O Unit for those words that are accessed by the

instruction. An immediate refresh instruction refreshes eight bits simulta-

neously (leftmost or rightmost eight bits) in addition to the specified bit.

Immediate refresh instructions cannot be used for Units on Slave Racks.

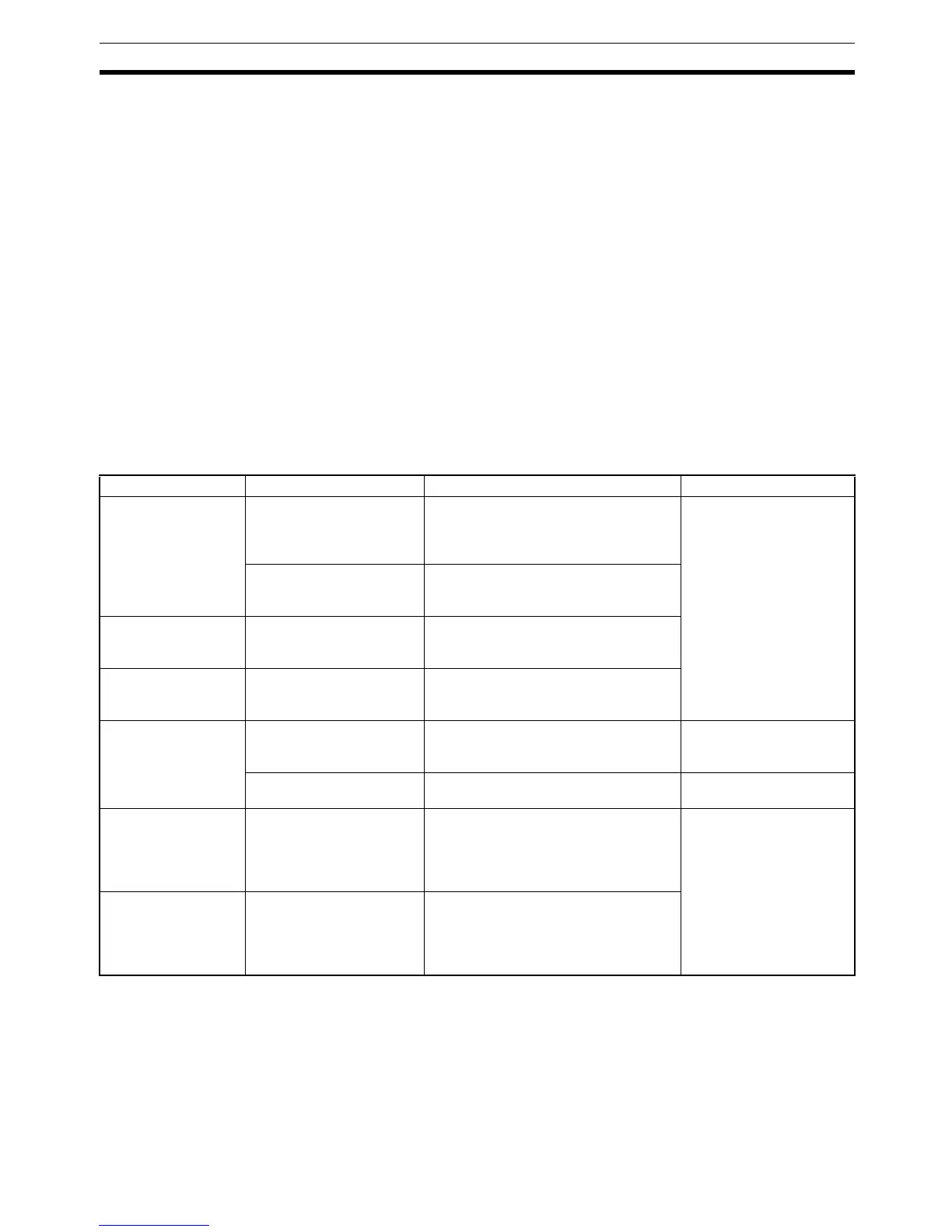

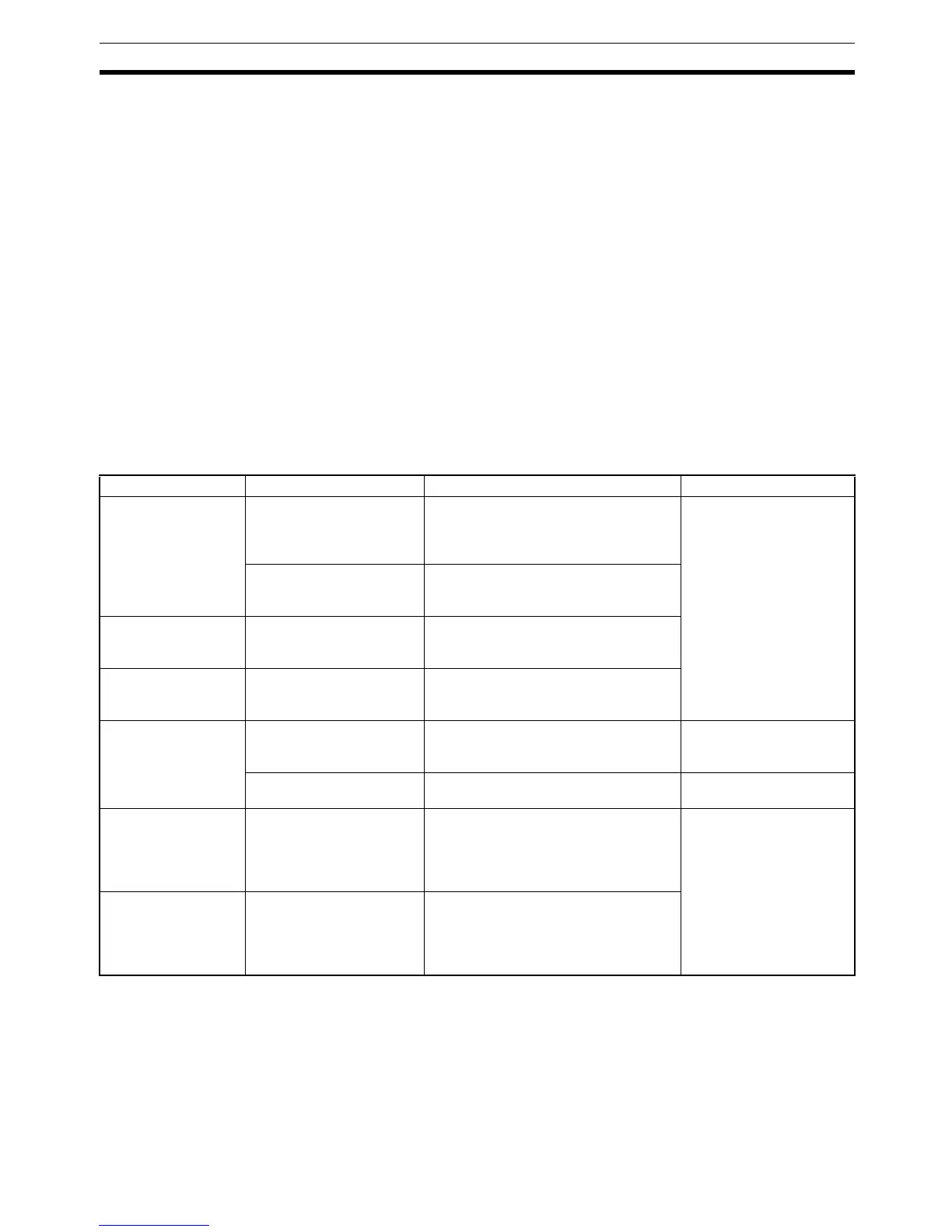

Instruction variation Mnemonic Function I/O refresh

Ordinary LD, AND, OR, LD NOT,

AND NOT, OR NOT

The ON/OFF status of the specified bit

is taken by the CPU with cyclic refresh-

ing, and it is reflected in the next instruc-

tion execution.

Cyclic refreshing

OUT, OUT NOT After the instruction is executed, the ON/

OFF status of the specified bit is output

with the next cyclic refreshing.

Differentiated up @LD, @AND, @OR The instruction is executed once when

the specified bit turns from OFF to ON

and the ON state is held for one cycle.

Differentiated down %LD, %AND, %OR The instruction is executed once when

the specified bit turns from ON to OFF

and the ON state is held for one cycle.

Immediate refresh !LD, !AND, !OR, !LD NOT,

!AND NOT, !OR NOT

The input data for the specified bit is

taken by the CPU and the instruction is

executed.

Before instruction execu-

tion

!OUT, !OUT NOT After the instruction is executed, the

data for the specified bit is output.

After instruction execution

Differentiated up /

immediate refresh

!@LD, !@AND, !@OR The input data for the specified bit is

refreshed by the CPU, and the instruc-

tion is executed once when the bit turns

from OFF to ON and the ON state is

held for one cycle.

Before instruction execu-

tion

Differentiated down /

immediate refresh

!%LD, !%AND, !%OR The input data for the specified bit is

refreshed by the CPU, and the instruc-

tion is executed once when the bit turns

from ON to OFF and the ON state is

held for one cycle.

Loading...

Loading...