692

Double-precision Floating-point Instructions (CS1-H, CJ1-H, CJ1M, or CS1D Only) Section 3-16

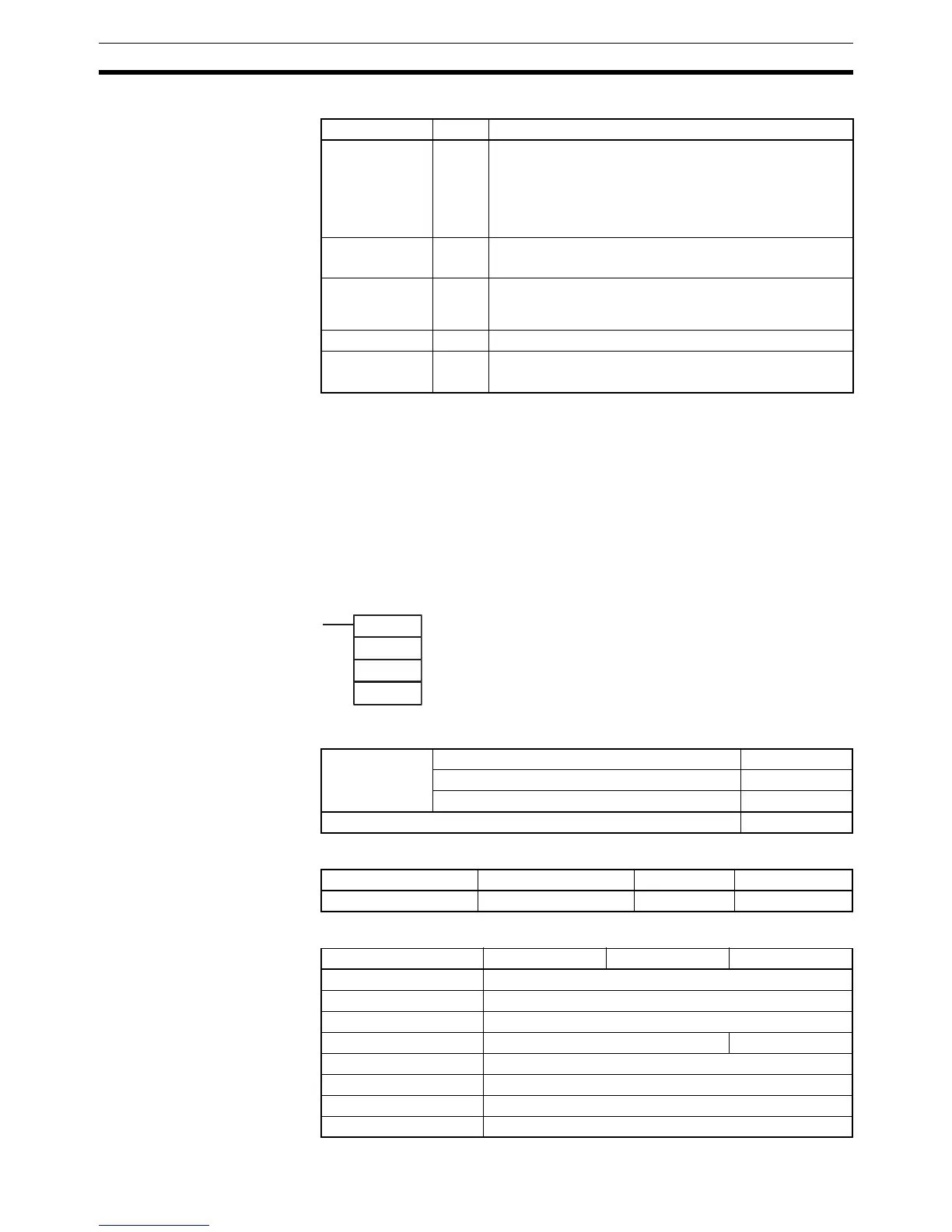

Flags

Precautions The source data in words S to S+3 must be in IEEE754 floating-point data for-

mat.

3-16-20DOUBLE EXPONENTIAL POWER: PWRD(860)

Purpose Raises a double-precision (64-bit) floating-point number to the power of

another double-precision (64-bit) floating-point number.

This instruction is supported by CS1-H, CJ1-H, CJ1M, and CS1D CPU Units

only.

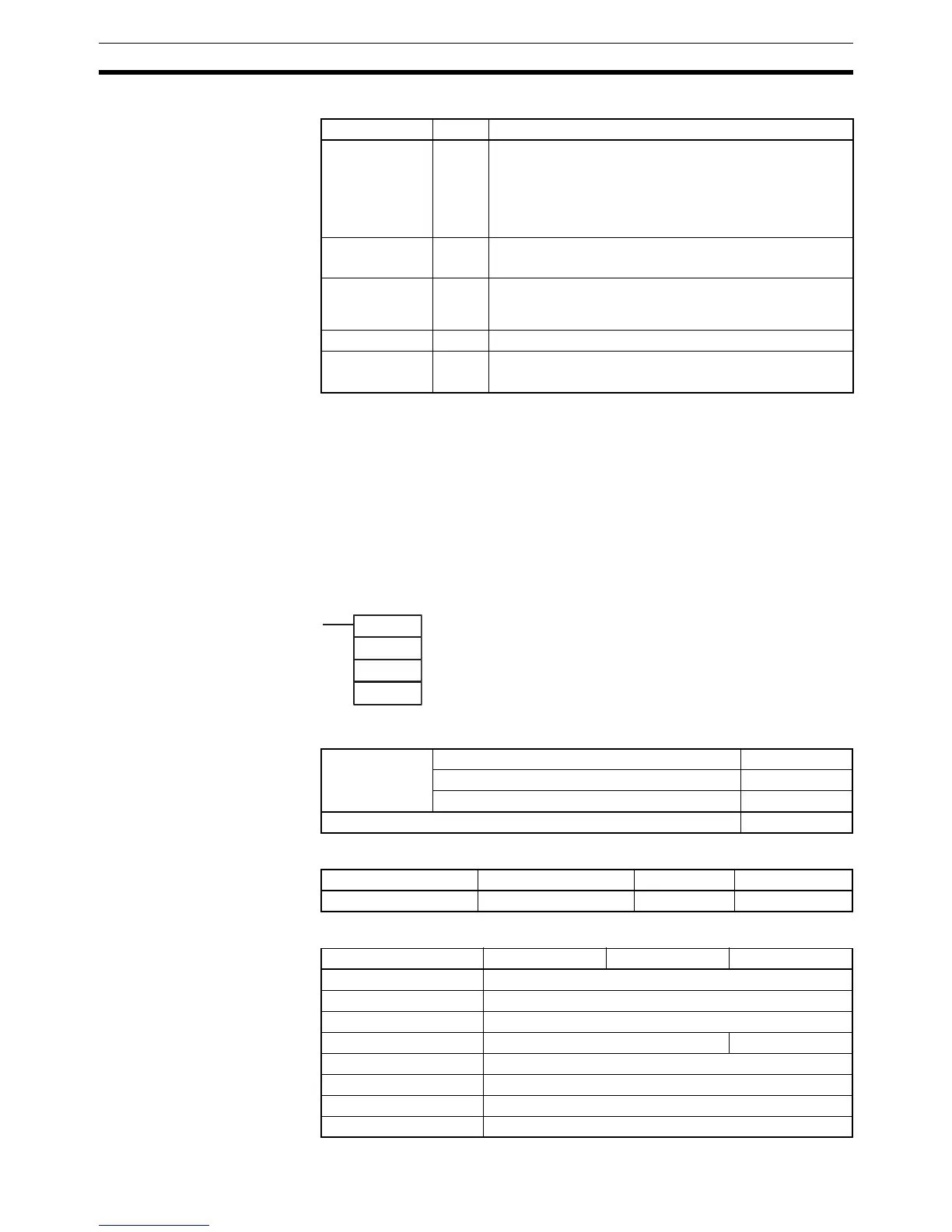

Ladder Symbol

Variations

Applicable Program Areas

Operand Specifications

Name Label Operation

Error Flag ER ON if the source data is not recognized as floating-point

data.

ON if the source data is negative.

ON if the source data is not a number (NaN).

OFF in all other cases.

Equals Flag = ON if both the exponent and mantissa of the result are 0.

OFF in all other cases.

Overflow Flag OF ON if the absolute value of the result is too large to be

expressed as a double-precision (64-bit) floating-point

value.

Underflow Flag UF Unchanged

Negative Flag N ON if the result is negative.

OFF in all other cases.

PWRD(860)

B

E

D

B: First base word

E: First exponent word

D: First destination word

Variations Executed Each Cycle for ON Condition PWRD(860)

Executed Once for Upward Differentiation @PWRD(860)

Executed Once for Downward Differentiation Not supported.

Immediate Refreshing Specification Not supported.

Block program areas Step program areas Subroutines Interrupt tasks

OK OK OK OK

Area B E D

CIO Area CIO 0000 to CIO 6140

Work Area W000 to W508

Holding Bit Area H000 to H508

Auxiliary Bit Area A000 to A956 A448 to A956

Timer Area T0000 to T4092

Counter Area C0000 to C4092

DM Area D00000 to D32764

EM Area without bank E00000 to E32764

Loading...

Loading...