13. Timer S

puorG92/C61M

page 155

854fo7002,03.raM21.1.veR

2110-1010B90JER

13.1.1 Base Timer Reset Register(G1BTRR)

The G1BTRR register provides the capability to reset the base timer when the base timer count value

matches the value stored in the G1BTRR register. The G1BTRR register is enabled by the RST4 bit

in the G1BCR0 register. This function is identical in operation to the G1PO0 base timer reset that is

enabled by the RST1 bit in the G1BCR0 reigster. If the free-running operation is not selected, the

channel 0 can be used for a waveform generation when the base timer is reset by the G1BTRR

register. Do not enable bits RST1 and RST4 simultaneously.

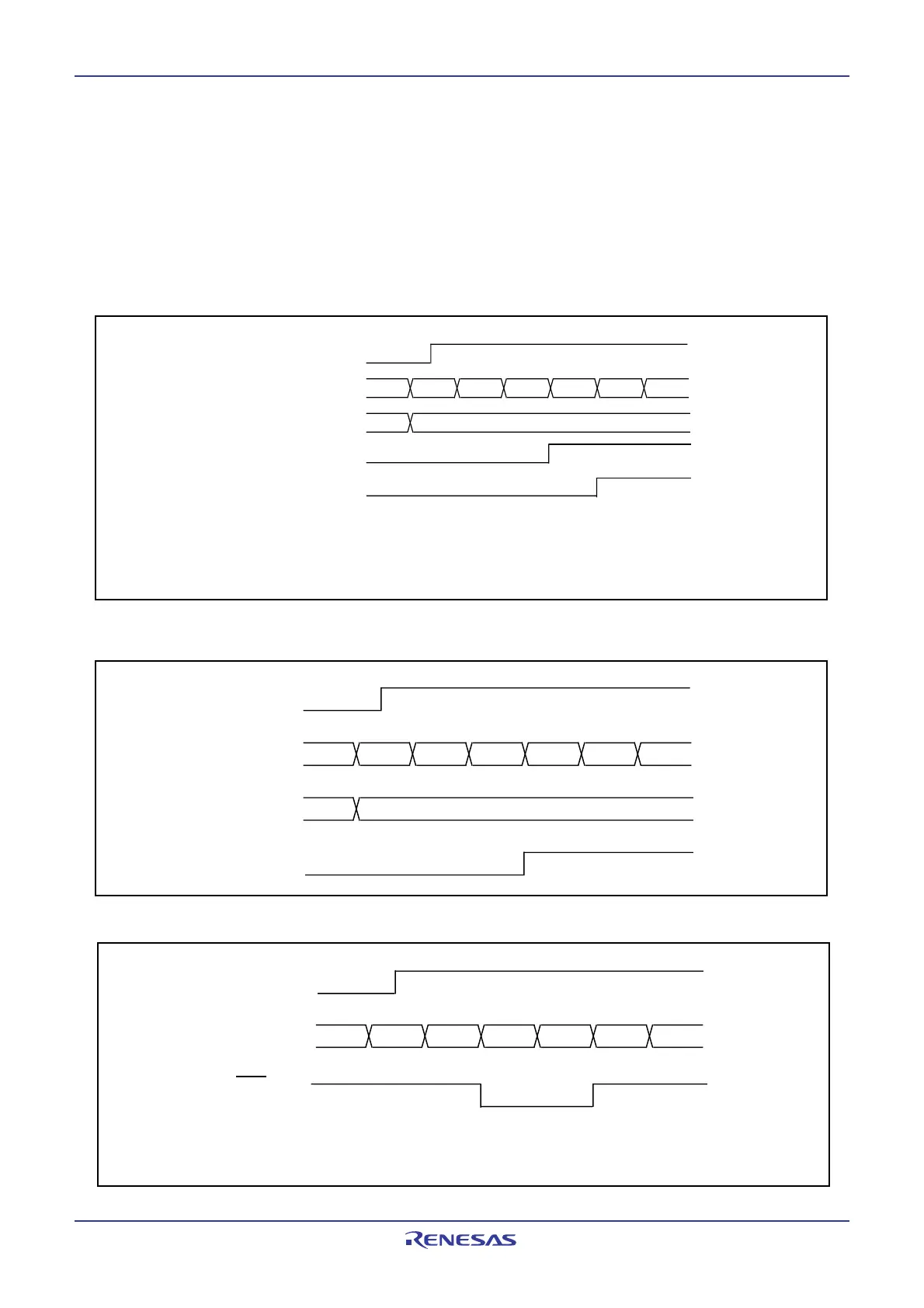

Figure 13.15 Base Timer Reset operation by Base Timer Reset Register

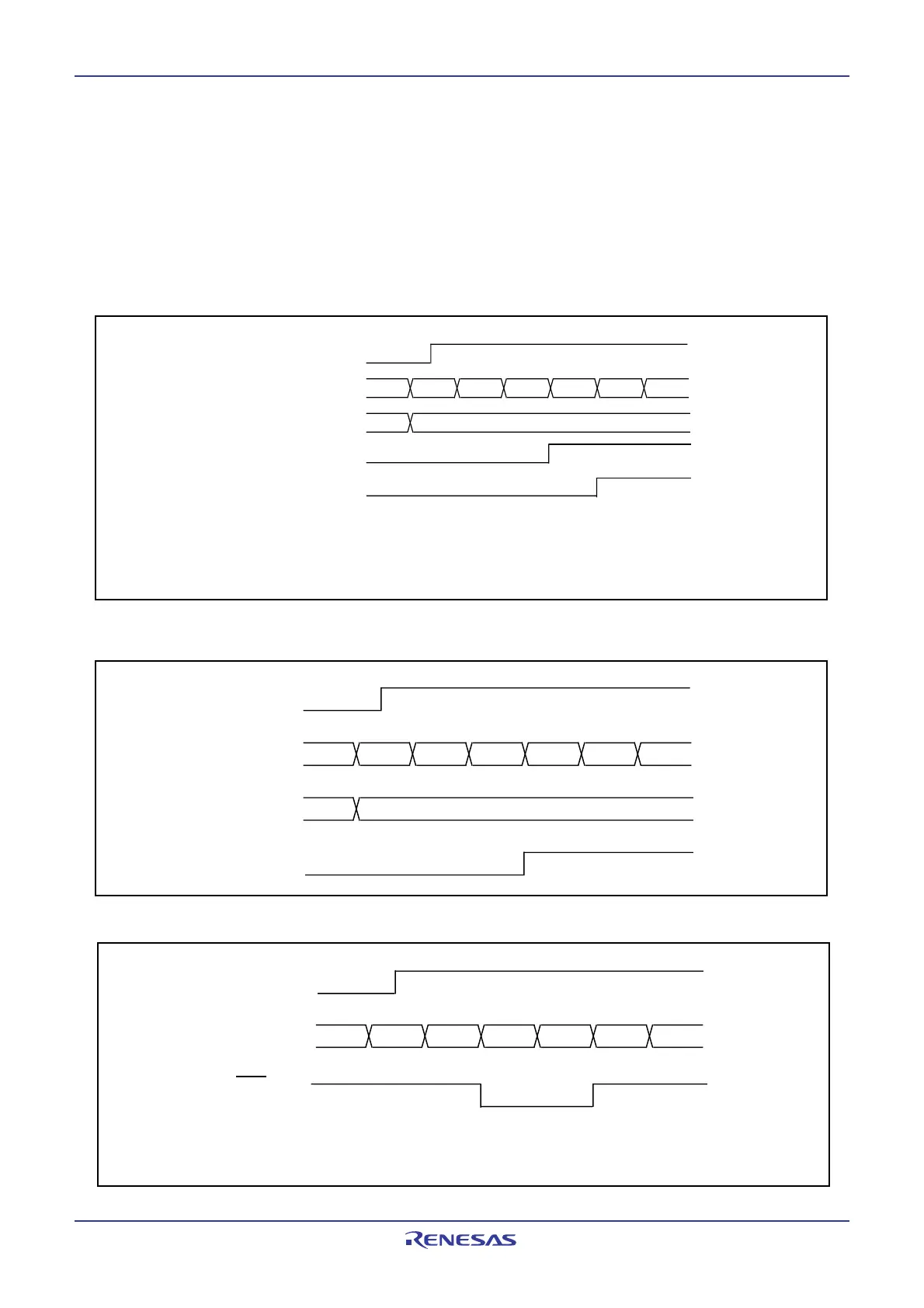

Figure 13.16 Base Timer Reset operation by G1PO0 register

_______

Figure 13.17 Base Timer Reset operation by INT1

NOTE:

________ ________

1. INT1 Base Timer reset does not generate a Base Timer interrupt. INT1 may generate an interrupt if enabled.

Base timer

G1BTRR register

(Base timer reset register)

Base timer interrupt

RST4

m - 2 m - 1 m m + 1 0000

16

m

Base timer overflow request

(1)

NOTE:

1. Following conditions are required to generate a base timer overflow request by resetting the base timer.

If the IT bit is set to 0: 07FFF

16 ≤ m ≤ 0FFFE16

If the IT bit is set to 1: 07FFF16 ≤ m ≤ 0FFFE16 or 0BFFF16 ≤ m ≤ 0FFFE16

0001

16

Base timer

G1PO0

G1IR0

RST1

m - 2 m - 1 m m + 1 0000

16

m

0001

16

RST2

Base timer

P83/INT1

m - 2 m - 1 m m + 1 000016 000116

Loading...

Loading...