18. CRC Calculation Circuit

puorG92/C61M

page 313

854fo7002,03.raM21.1.veR

2110-1010B90JER

18. CRC Calculation Circuit

The Cyclic Redundancy Check (CRC) calculation detects errors in blocks of data. The MCU uses a gen-

erator polynomial of CRC_CCITT (X

16

+ X

12

+ X

5

+ 1) or CRC-16 (X

16

+ X

15

+ X

2

+ 1) to generate CRC

code.

The CRC code is a 16-bit code generated for a block of a given data length in multiples of bytes. The code

is updated in the CRC data register everytime one byte of data is transferred to a CRC input register. The

data register must be initialized before use. Generation of CRC code for one byte of data is completed in

two machine cycles.

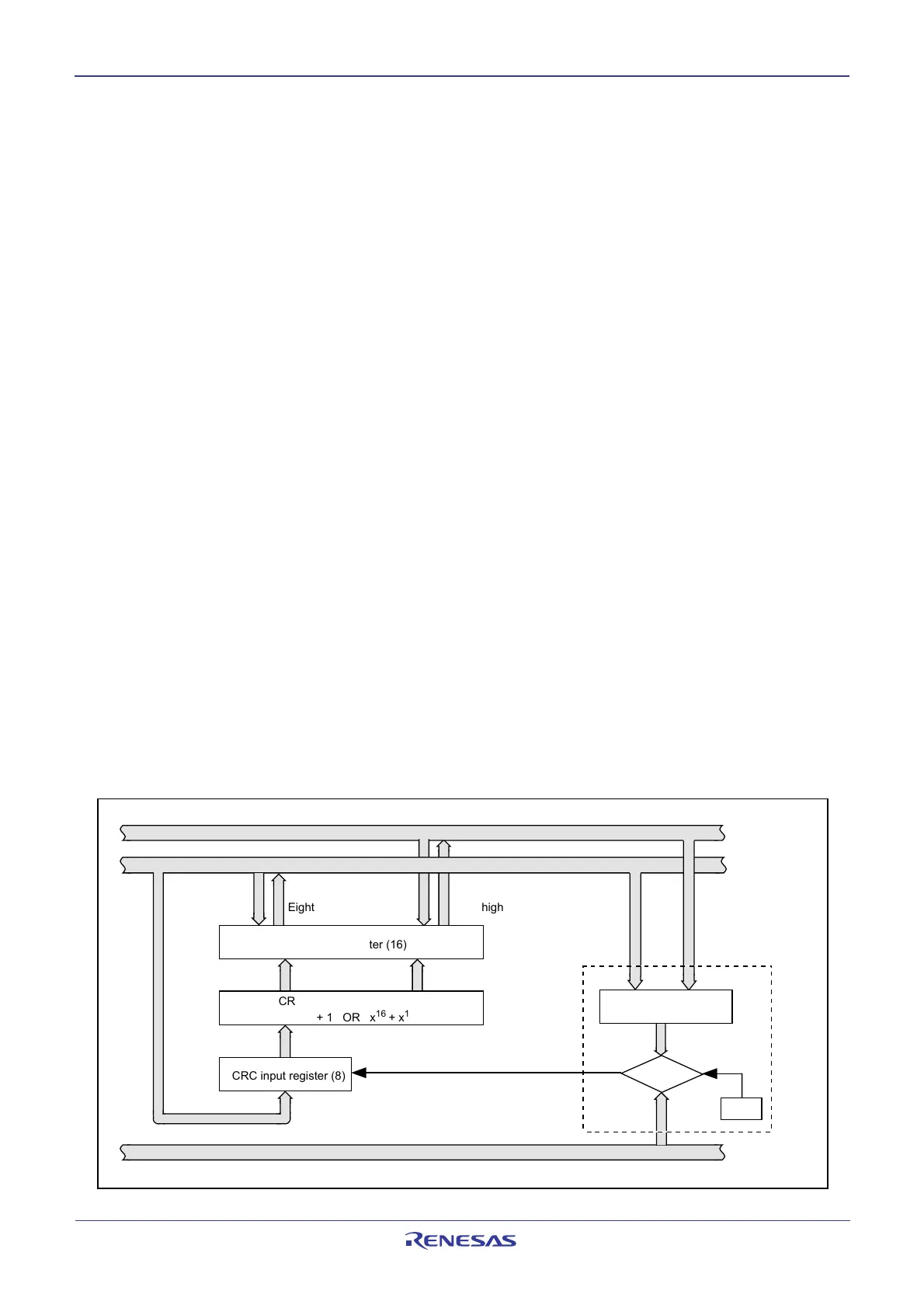

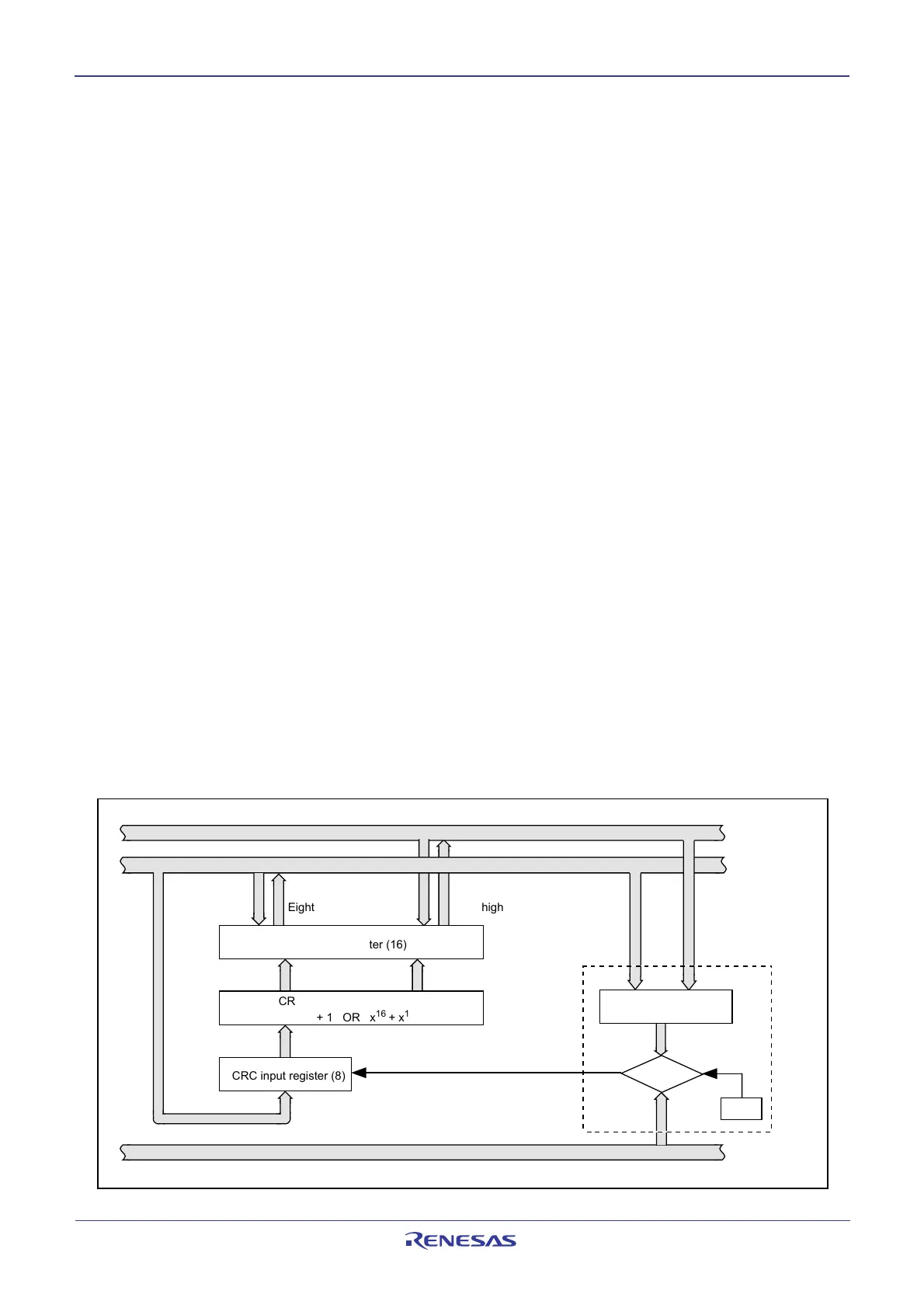

Figure 18.1 shows the block diagram of the CRC circuit. Figure 18.2 shows the CRC-related registers.

Figure 18.3 shows the calculation example using the CRC_CCITT operation.

18.1 CRC Snoop

The CRC circuit includes the ability to snoop reads and writes to certain SFR addresses. This can be used

to accumulate the CRC value on a stream of data without using extra bandwidth to explicitly write data into

the CRCIN register. All SFR addresses after 002016 are subject to the CRC snoop. The CRC snoop is

useful to snoop the writes to a UART TX buffer, or the reads from a UART RX buffer.

To snoop an SFR address, the target address is written to the CRC snoop Address Register (CRCSAR).

The two most significant bits of this register enable snooping on reads or writes to the target address. If the

target SFR is written to by the CPU or DMA, and the CRC snoop write bit is set (CRCSW=1), the CRC will

latch the data into the CRCIN register. The new CRC code will be set in the CRCD register.

Similarly, if the target SFR is read by the CRC or DMA, and the CRC snoop read bit is set (CRCSR=1), the

CRC will latch the data from the target into the CRCIN register and calculate the CRC.

The CRC circuit can only calculate CRC codes on data byte at a time. Therefore, if a target SFR is

accessed in word (16 bit), only one low-order byte data is stored into the CRCIN register.

Figure 18.1 CRC circuit block diagram

Eight low-order bits

Eight high-order bits

Data bus high-order

Data bus low-order

CRCD register (16)

CRC input register (8)

CRC code generating circuit

x

16

+ x

12

+ x

5

+ 1 OR x

16

+ x

15

+ x

2

+ 1

Address Bus

SnoopB

lock

Snoop

enable

Snoop Address

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

Equal?

(Address 03BD16, 03BC16)

(Address 03BE

16)

Loading...

Loading...