13. Timer S

puorG92/C61M

page 156

854fo7002,03.raM21.1.veR

2110-1010B90JER

13.2 Interrupt Operation

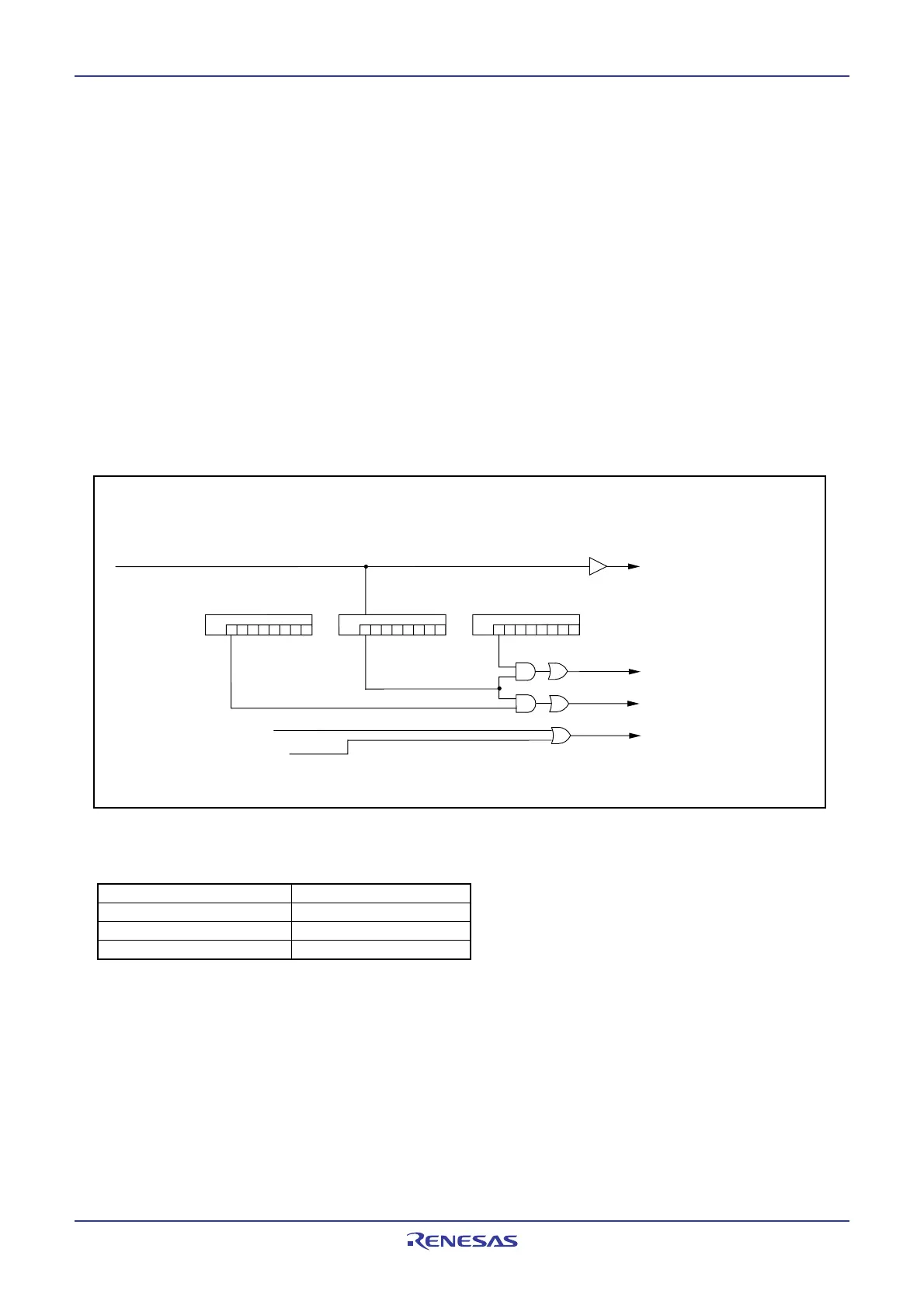

The IC/OC interrupt contains several request causes. Figure 13.18 shows the IC/OC interrupt block dia-

gram and Table 13.4 shows the IC/OC interrupt assignation.

When either the base timer reset request or base timer overflow request is generated, the IR bit in the BTIC

register corresponding to the IC/OC base timer interrupt is set to 1 (with an interrupt request). Also when an

interrupt request in each eight channels (channel i) is generated, the bit i in the G1IR register is set to 1 (with

an interrupt request). At this time, if the bit i in the G1IE0 register is 1 (IC/OC interrupt 0 request enabled),

the IR bit in the ICOC0IC register corresponding to the IC/OC interrupt 0 is set to 1 (with an interrupt

request). And if the bit i in the G1IE1 register is 1 (IC/OC interrupt 1 request enabled), the IR bit in the

ICOC1IC register corresponding to the IC/OC interrupt 1 is set to 1(with an interrupt request).

Additionally, because each bit in the G1IR register is not automatically set to 0 even if the interrupt is

acknowledged, set to 0 by program. If these bits are left as 1, all IC/OC channel interrupt causes, which are

generated after setting the IR bit to 1, will be disabled.

Figure 13.18 IC/OC Interrupt and DMA request generation

Table 13.4 Interrupt Assignment

Interrupt Interrupt control register

IC/OC base timer interrupt BTIC(004716)

IC/OC interrupt 0 ICOC0IC(004516)

IC/OC interrupt 1 ICOC0IC(0046

16)

13.3 DMA Support

Each of the interrupt sources - the eight IC/OC channel interrupts and the one Base Timer interrupt - are

capable of generating a DMA request.

Interrupt Select Logic

Channel 0 to 7 Interrupt re

quests

DMA Requests (channel 0 to

7)

All register are read / write

G1IE0

G1IR

G1IE1

IC/OC interrupt 1 request

IC/OC interrupt 0 request

IC/OC base timer interrupt req

uest

Base timer reset request

Base timer overflow request

Base Timer Interrupt / DMA Request

ENABLE REQUEST

ENABLE

Loading...

Loading...