20. Flash Memory Version

puorG92/C61M

page 337

854fo7002,03.raM21.1.veR

2110-1010B90JER

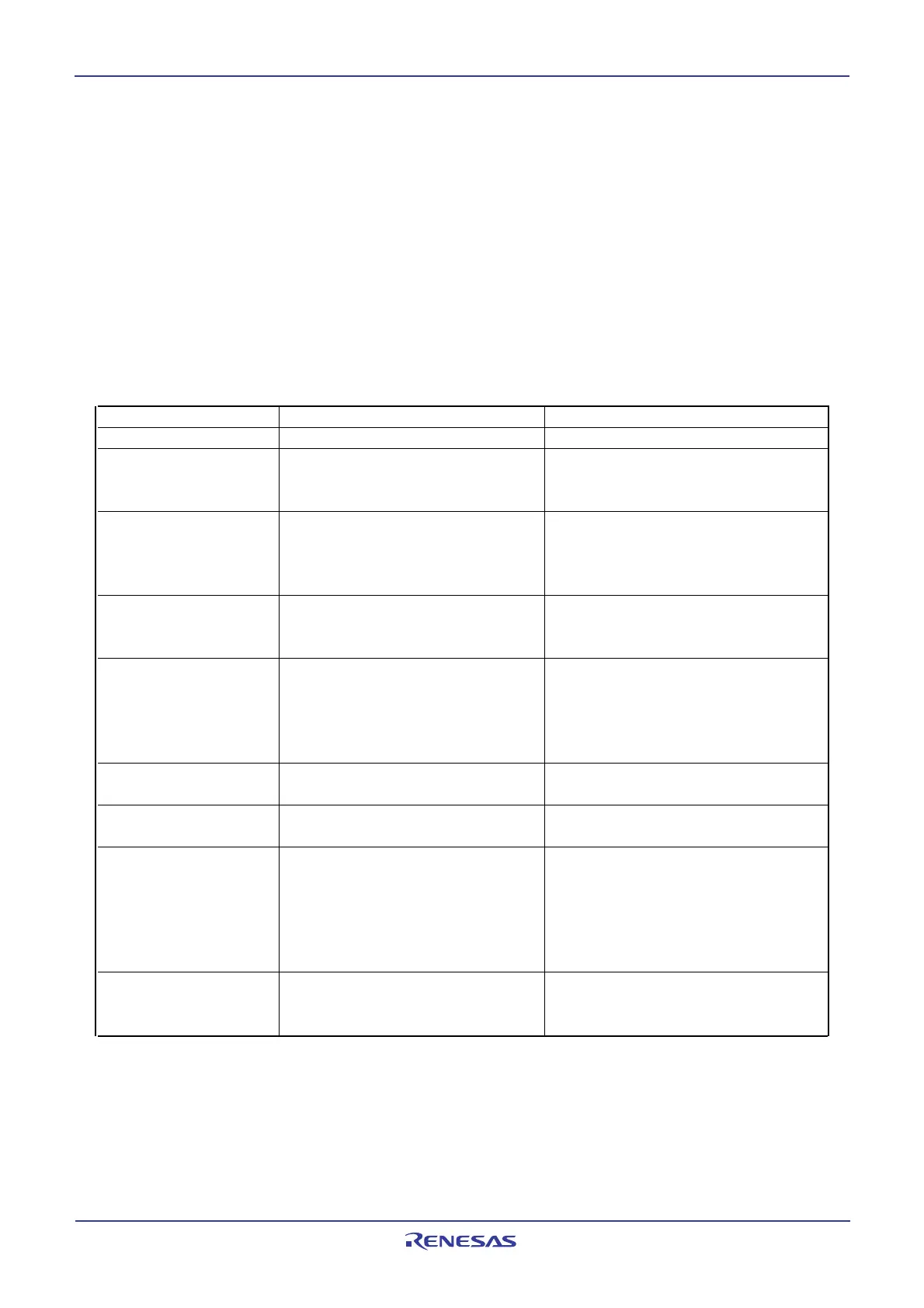

Item EW mode 0 EW mode 1

Operation mode Single chip mode Single chip mode

Areas in which a User ROM area User ROM area

rewrite control

program can be located

Areas where The rewrite control program must be The rewrite control program can be

rewrite control transferred to any other than the flash excuted in the user ROM area

program can be memory (e.g., RAM) before being

executed

(2)

executed

Areas which can be User ROM area User ROM area

rewritten However, this excludes blocks with the

rewrite control program

Software command None • Program, block erase command

Restrictions Cannot be executed in a block having

the rewite control program

• Read Status Register command

Cannot be executed

Mode after programming Read Status Register Mode Read Array mode

or erasing

CPU state during auto- Operating In a hold state (I/O ports retain the state

write and auto-erase before the command is excuted

(1)

Flash memory status • Read the FMR00, FMR06, and Read the FMR00, FMR06, and FMR07

detection FMR07 bits in the FMR0 register bits in the FMR0 registerby program

by program

• Execute the read status register

command to read bits SR7, SR5,

and SR4.

Condition for transferring

Set bits FMR40 and FMR41 in The FMR40 bit in the FMR4 register is

to erase-suspend

(3)

the FMR4 register to 1 by program. set to 1 and the interruput request of

an acknowledged interrupt is generated

NOTES:

1. Do not generate a DMA transfer.

2. Block 1 and Block 0 are enabled for rewrite by setting FMR02 bit in the FMR0 register to 1 and setting

FMR16 bit in the FMR1 register to 1. Block 2 to Block 5 are enabled for rewrite by setting FMR16 bit

in the FMR1 register to 1.

3. The time, until entering erase suspend and reading flash is enabled, is maximum

td(SR-ES)

after

satisfying the conditions.

20.4 CPU Rewrite Mode

In CPU rewrite mode, the user ROM area can be rewritten when the CPU executes software commands.

The user ROM area can be rewritten with MCU mounted on a board without using the ROM writer. The

program and block erase commands are executed only in the user ROM area.

When the interrupt requests are generated during the erase operation in CPU rewirte mode, the flash

memory offers an erase suspend function to suspend the erase operation and process the interrupt opera-

tion. During the erase suspend function is operated, the user ROM area can be read by program.

Erase-write(EW) 0 mode and erase-write 1 mode are provided as CPU rewrite mode. Table 20.3 lists

differences between EW mode 0 and EW mode 1. One wait is required for the CPU erase-write control.

Table 20.3 EW Mode 0 and EW Mode 1

Loading...

Loading...