puorG92/C61M

22. Usage Notes

page 443

854fo7002,03.raM21.1.veR

2110-1010B90JER

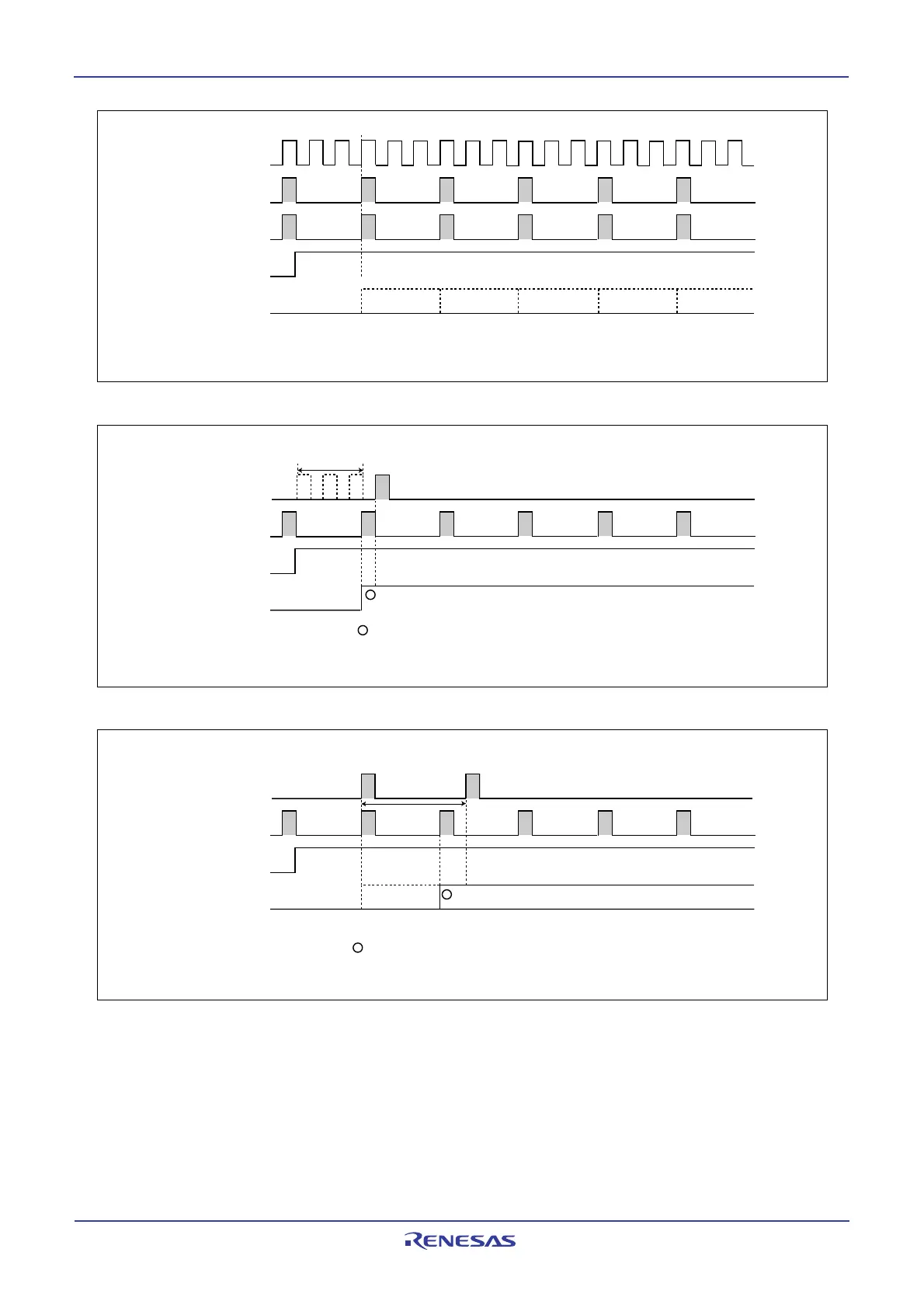

Figure 22.5 When Updating Period of CAN Module Matches Access Period from CPU

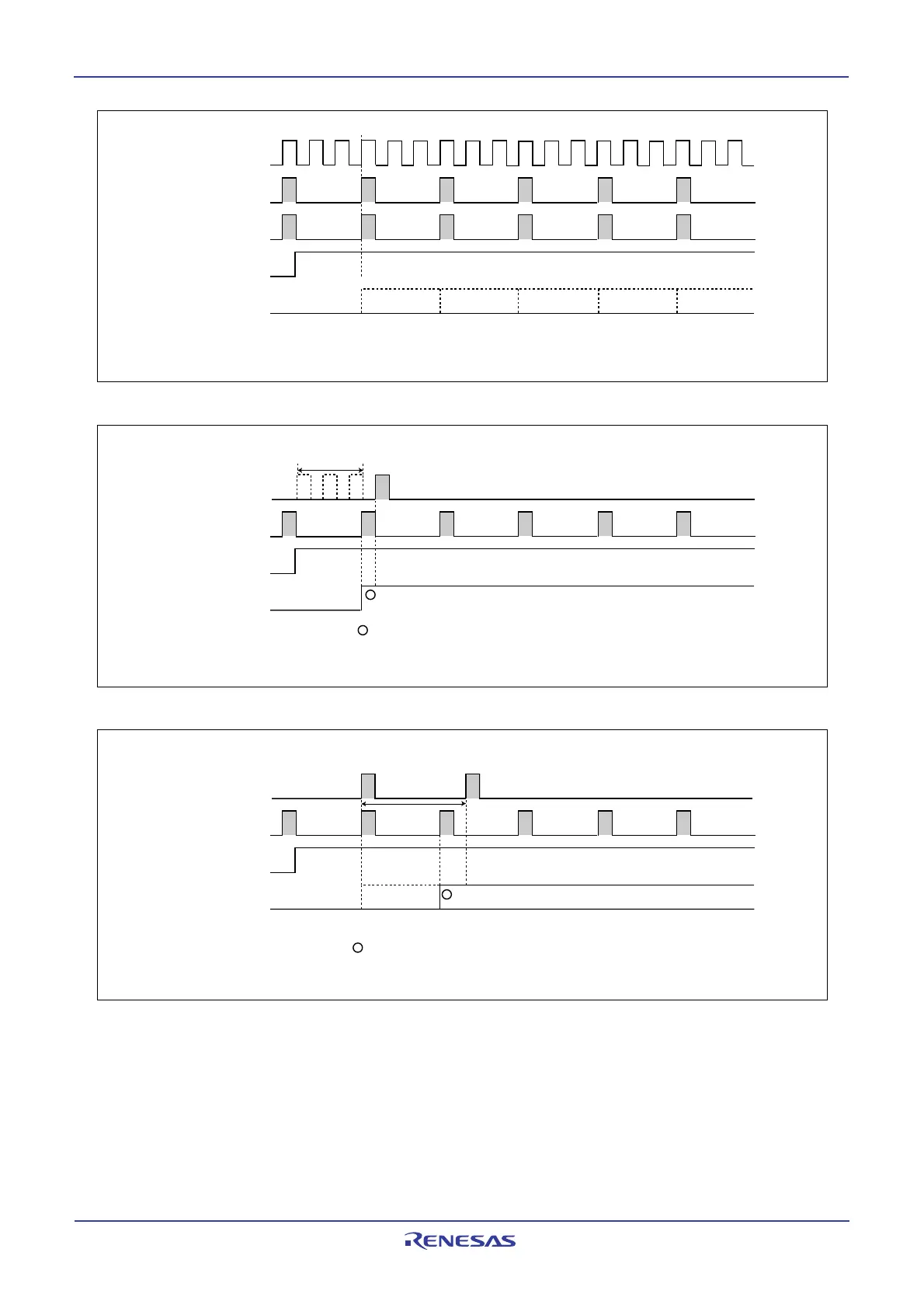

Figure 22.6 With a Wait Time of 3fCAN Before CPU Read

Figure 22.7 When Polling Period of CPU is 3fCAN or Longer

f

CAN

✕: When the CAN module’s State_Reset bit updating period matches the CPU’s read

period, it does not enter reset mode, for the CPU read has the higher priority.

✕✕✕ ✕✕

CPU read signal

CPU reset signal

Updating period of

CAN module

C0STR register

b8: State_Reset bit

0: CAN operation

mode

1: CAN reset/initial-

ization mode

: Updated without fail in period of 3f

CAN

CPU read signal

CPU reset signal

Updating period of

the CAN module

C0STR register

b8: State_Reset bit

Wait time

0: CAN operation

mode

1: CAN reset/initial-

ization mode

CPU read signal

CPU reset signal

Updating period of

the CAN module

C0STR register

b8: State_Reset bit

✕

4f

CAN

0: CAN operation

mode

1: CAN reset/initial-

ization mode

: Updated without fail in period of 4fCAN

✕: When the CAN module’s State_Reset bit updating period matches the CPU’s read

period, it does not enter reset mode, for the CPU read has the higher priority.

Loading...

Loading...