58 www.xilinx.com RocketIO™ Transceiver User Guide

UG024 (v3.0) February 22, 2007

Chapter 2: Digital Design Considerations

R

Additional reset and power control descriptions are given in Table 2-8 and Table 2-9.

VHDL Template

-- Module: gt_reset

-- Description: VHDL submodule

-- reset for GT

--

-- Device: Virtex-II Pro Family

---------------------------------------------------------------------

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.Numeric_STD.all;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

--

-- pragma translate_off

library UNISIM;

use UNISIM.VCOMPONENTS.ALL;

-- pragma translate_on

--

entity gt_reset is

port (

USRCLK2_M : in std_logic;

LOCK : in std_logic;

REFCLK : out std_logic;

DCM_LOCKED: in std_logic;

RST : out std_logic);

end gt_reset;

--

architecture RTL of gt_reset is

--

signal startup_count : std_logic_vector (7 downto 0);

begin

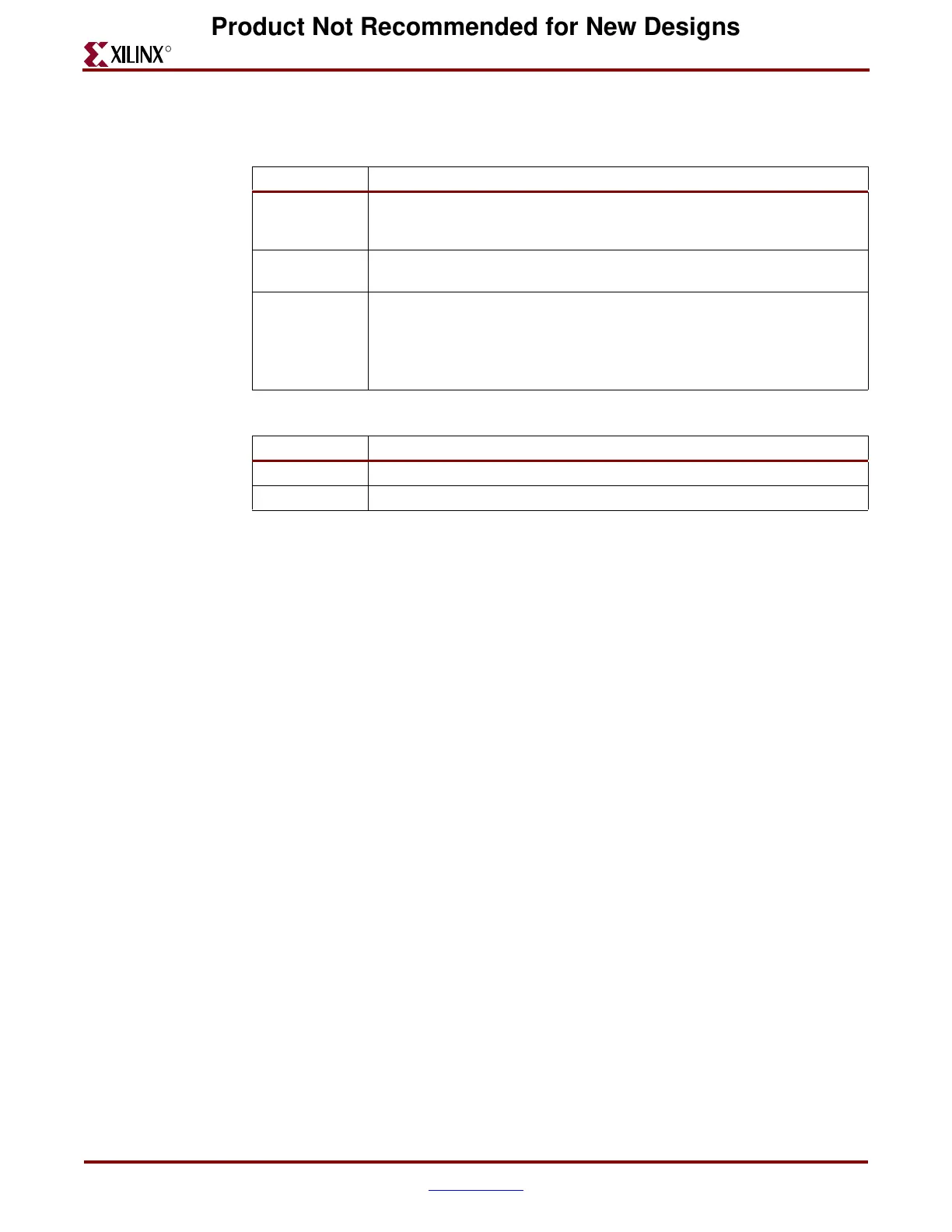

Table 2-8: Reset and Power Control Descriptions

Ports Description

RXRESET Synchronous receive system reset recenters the receiver elastic buffer, and resets

the 8B/10B decoder, comma detect, channel bonding, clock correction logic,

and other receiver registers. The PLL is unaffected.

TXRESET Synchronous transmit system reset recenters the transmission FIFO, and resets

the 8B/10B encoder and other transmission registers. The PLL is unaffected.

POWERDOWN Shuts down the transceiver (both RX and TX sides).

In POWERDOWN mode, transmit output pins TXP/TXN are not driven, but

biased by the state of transmit termination supply VTTX. If VTTX is not

powered, TXP/TXN float to a high-impedance state. Receive input pins

RXP/RXN respond similarly to the state of receive termination supply VTRX.

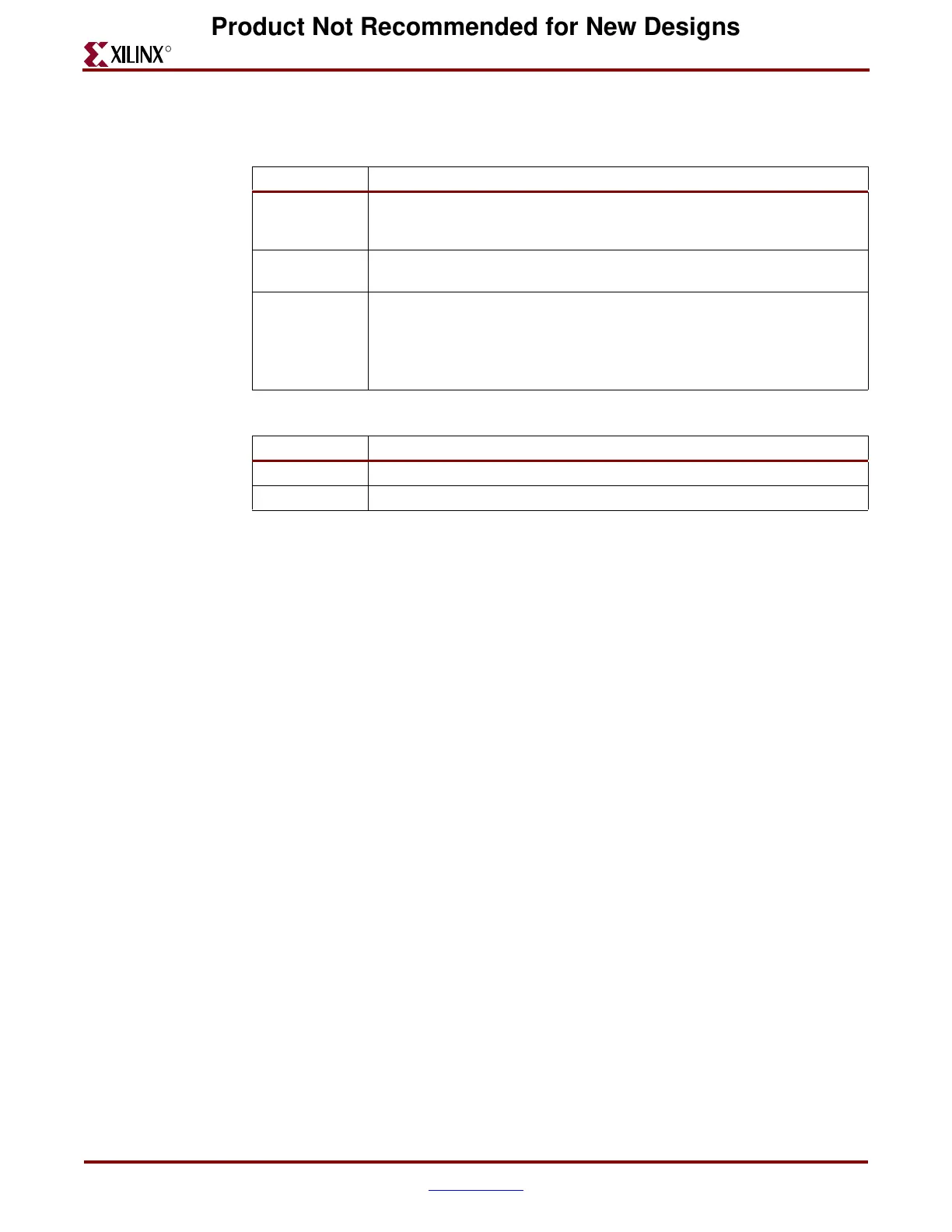

Table 2-9: Power Control Descriptions

POWERDOWN Transceiver Status

0 Transceiver in operation

1 Transceiver temporarily powered down

Notes:

1. Unused transceivers are automatically configured as powered-down by the implementation tools.

Product Not Recommended for New Designs

Loading...

Loading...