100 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 6: GTP Transmitter (TX)

R

There are no attributes in this section.

Description

Enabling 8B/10B Encoding

To disable the 8B/10B encoder on a given GTP transceiver, TXENC8B10BUSE must be

driven Low. To enable the 8B/10B encoder, TXENC8B10BUSE must be driven High. When

the encoder is turned off, the operation of the TXDATA port is as described in “FPGA TX

Interface.”

8B/10B Bit and Byte Ordering

The order of the bits after the 8B/10B encoder is the opposite of the order shown in

Appendix C, “8B/10B Valid Characters,” because 8B/10B encoding requires bit a0 to be

transmitted first, and the GTP transceiver always transmits the right-most bit first. To

match with 8B/10B, the 8B/10B encoder in the GTP transceiver automatically reverses the

bit order.

For the same reason, when a two-byte interface is used, the first byte to be transmitted

(byte 0) must be placed on TXDATA[7:0], and the second placed on TXDATA[15:8]. This

placement ensures that the byte 0 bits are all sent before the byte 1 bits, as required by

8B/10B encoding.

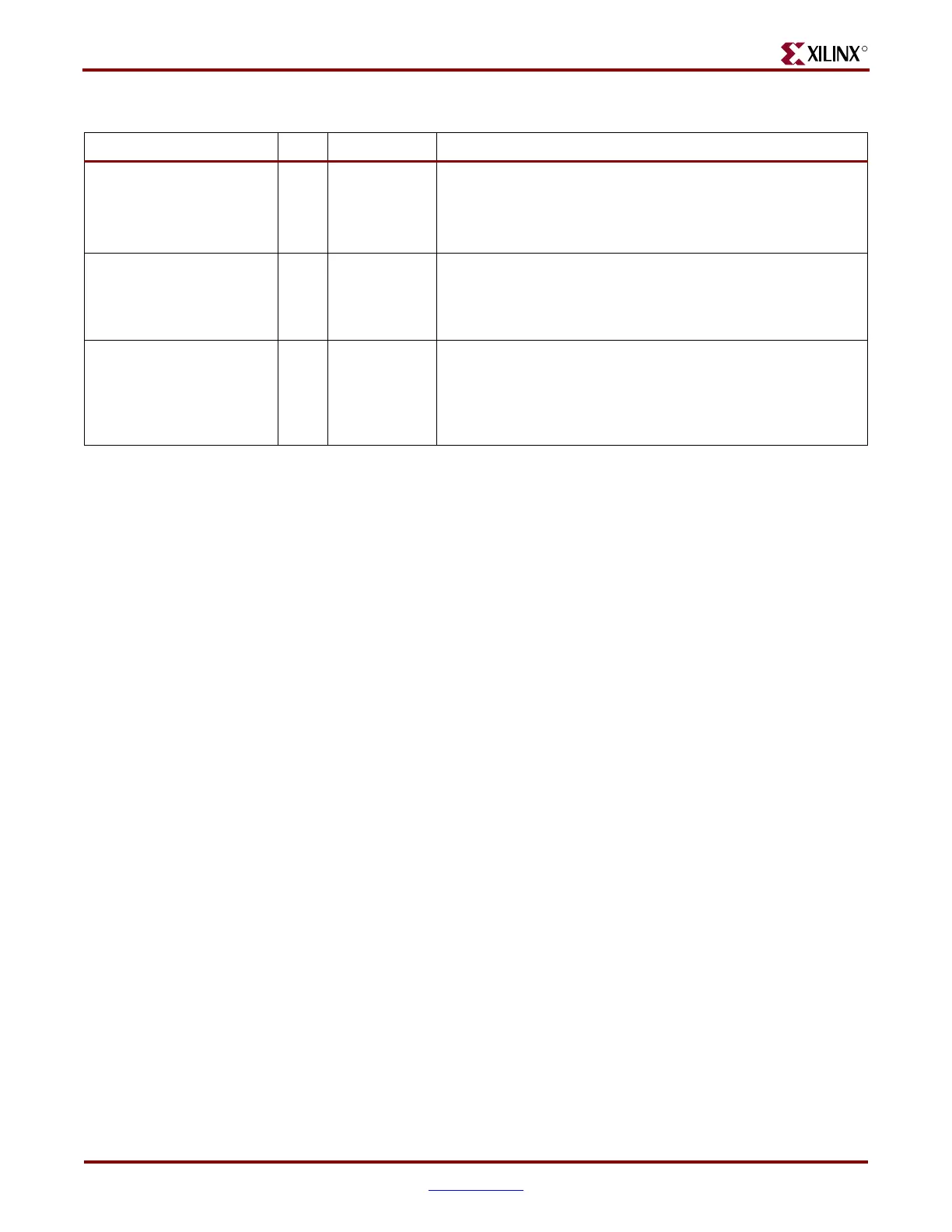

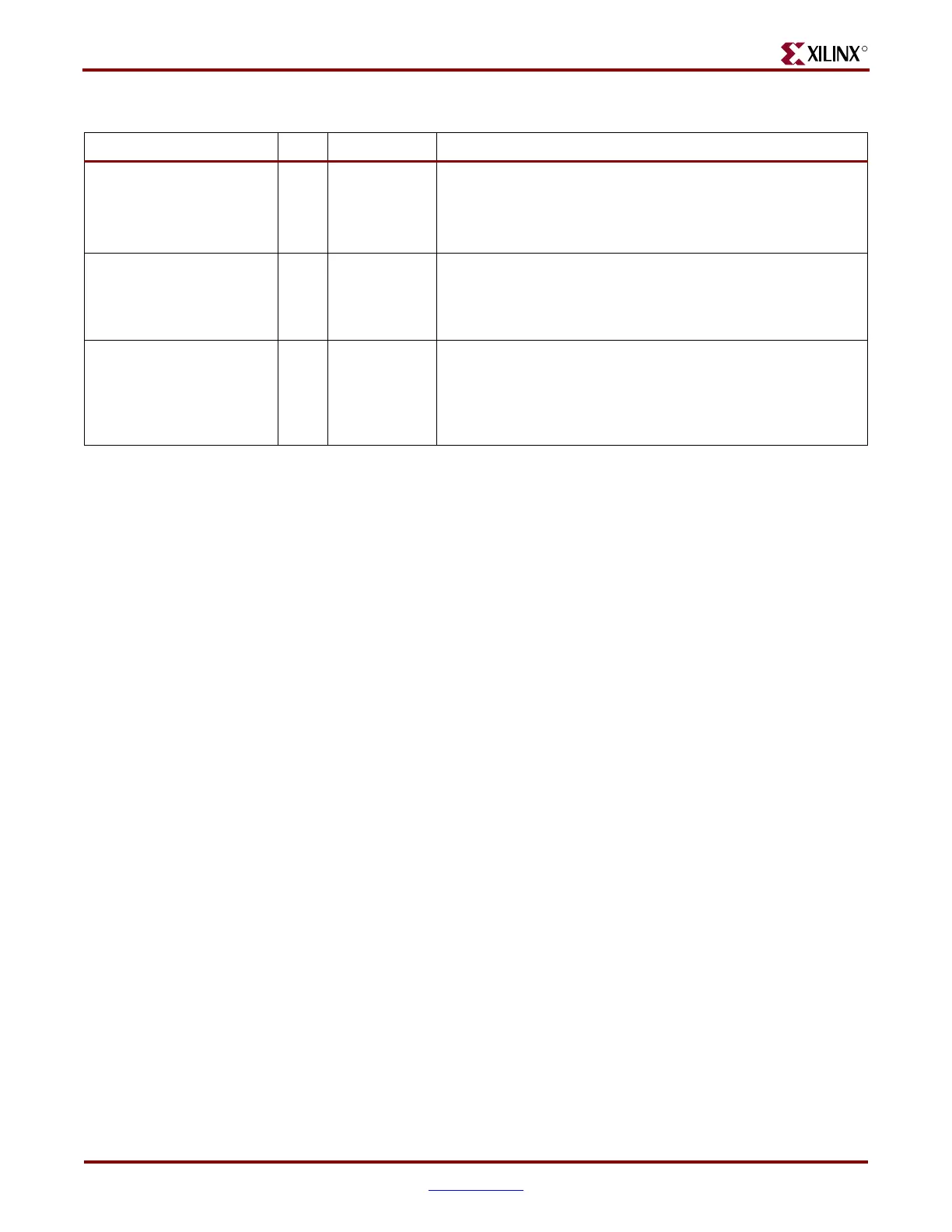

TXENC8B10BUSE0

TXENC8B10BUSE1

In TXUSRCLK2

TXENC8B10BUSE is set High to enable the 8B/10B encoder.

INTDATAWIDTH must also be High.

0: 8B/10B encoder bypassed. This option reduces latency.

1: 8B/10B encoder enabled. INTDATAWIDTH must be 1.

TXKERR0[1:0]

TXKERR1[1:0]

Out TXUSRCLK2

TXKERR indicates an invalid code for a K character was

specified.

TXKERR[1] corresponds to TXDATA[15:8], and TXKERR[0]

corresponds to TXDATA[7:0].

TXRUNDISP0[1:0]

TXRUNDISP1[1:0]

Out TXUSRCLK2

TXRUNDISP indicates the current running disparity of the

8B/10B encoder. This disparity corresponds to TXDATA clocked

in several cycles earlier.

TXRUNDISP[1] corresponds to previous TXDATA[15:8] data,

and TXRUNDISP[0] corresponds to previous TXDATA[7:0] data.

Table 6-4: TX Encoder Ports (Continued)

Port Dir Clock Domain Description

Loading...

Loading...