Virtex-5 RocketIO GTP Transceiver User Guide www.xilinx.com 187

UG196 (v1.3) May 25, 2007

R

Chapter 8

Cyclic Redundancy Check (CRC)

Overview

In Virtex-5 devices, each high-speed transceiver tile is paired with two CRC integrated

blocks. Each CRC block can operate independently as two 32-bit input CRC modules

(CRC32) or can be combined into a single 64-bit input CRC module (CRC64). The CRC

modules use the standard 32-bit Ethernet polynomial for CRC calculation. The CRC

integrated blocks are independent of the transceiver blocks.

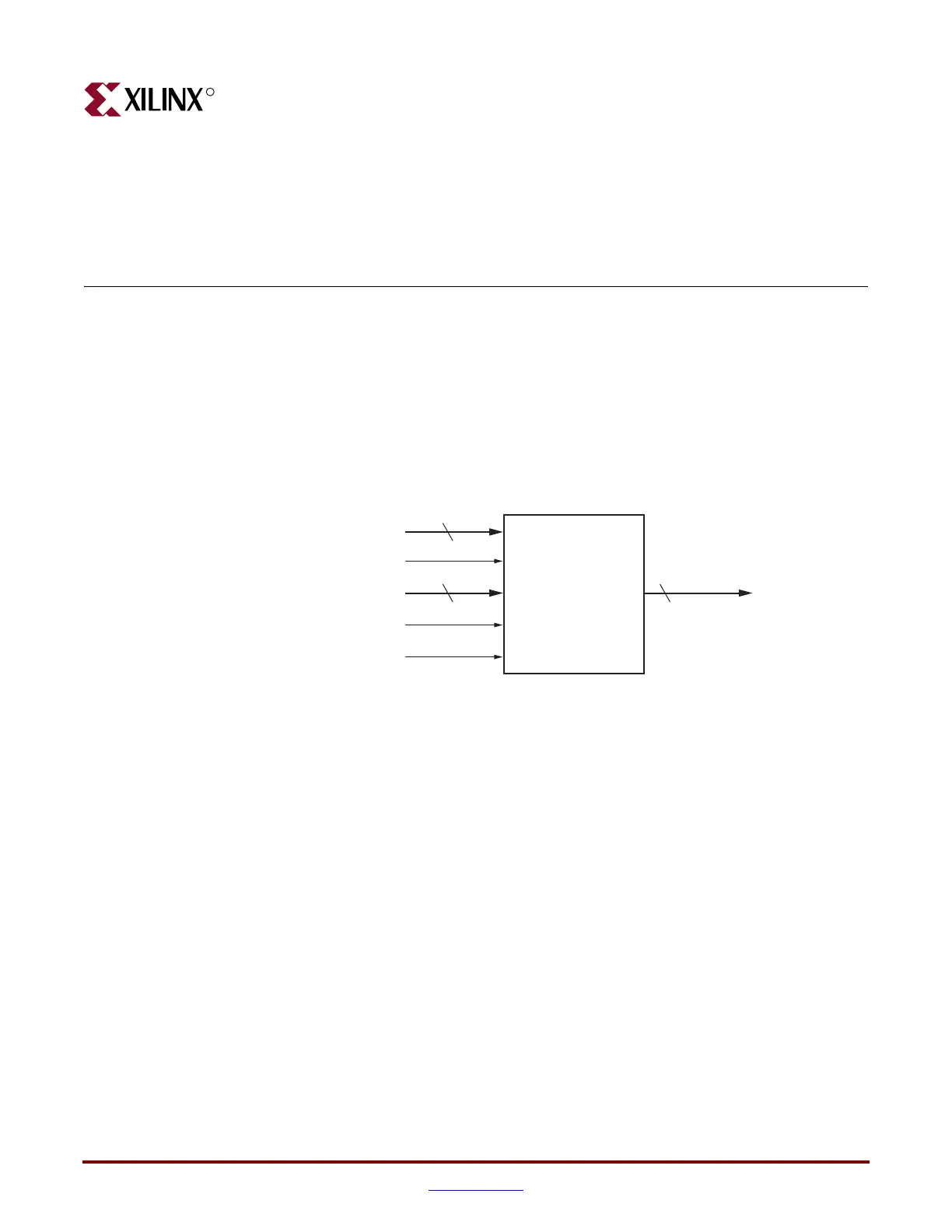

Figure 8-1 shows the basic port interface of the CRC block.

For clarification:

• Each GTP_DUAL tile is paired with two integrated CRC blocks.

• Each integrated CRC block can either operate as one 64-bit wide CRC module or as

two independent 32-bit wide CRC modules.

• For a given GTP_DUAL, four independent 32-bit wide CRC modules are only

possible when a 64-bit wide CRC module is not used.

Figure 8-2 shows how CRC modules are typically used in an application.

Figure 8-1: CRC Integrated Block

CRC Block

CRCOUT[31:0]

UG196_c8_01_100506

CRCIN[63/31:0]

CRCDATAVALID

CRCRESET

CRCCLK

CRCDATAWIDTH[2:0]

Loading...

Loading...