Virtex-5 RocketIO GTP Transceiver User Guide www.xilinx.com 183

UG196 (v1.3) May 25, 2007

FPGA RX Interface

R

There are no attributes in this section.

Description

The FPGA RX interface allows parallel received data to be read from the GTP transceiver.

For this interface to be used, the following must be done:

• The width of the RXDATA port must be configured

• RXUSRCLK2 and RXUSRCLK must be connected to clocks running at the correct rate.

Configuring the Width of the Interface

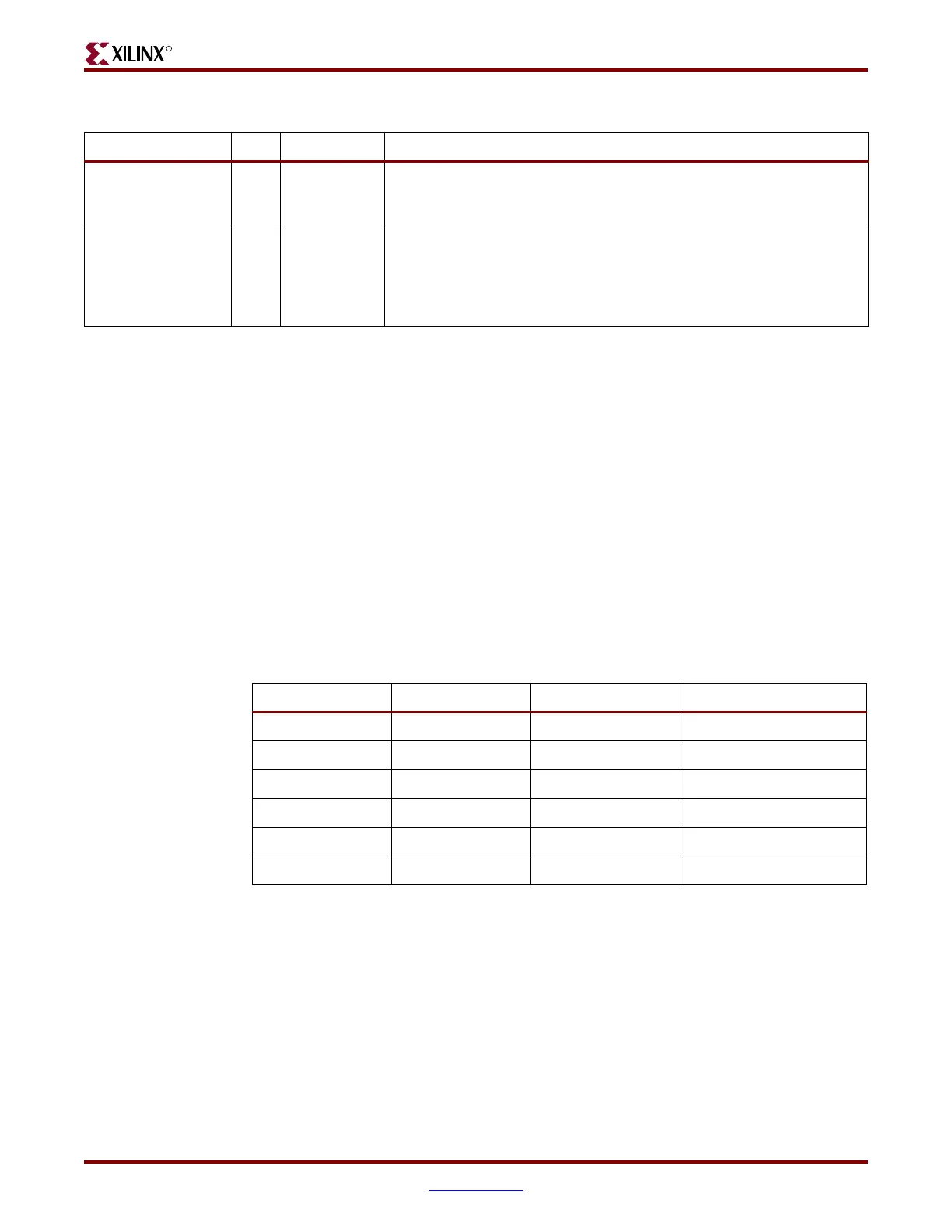

Table 7-35 shows how to select the interface width for the RX datapath. 8B/10B decoding is

discussed in more detail in “Configurable 8B/10B Decoder,” page 157.

RXUSRCLK0

RXUSRCLK1

In N/A

Input clock used for internal RX logic after the RX FIFO. Generally,

RXUSRCLK0/1 runs at either 1/8 or 1/10 the RX baud rate, which for

some standards is identical to TXUSRCLK0/1.

RXUSRCLK20

RXUSRCLK21

In N/A

Input clock used for the interface between the FPGA and the GTP

transceiver. For a one-byte interface, RXUSRCLK20/1 is equal to

RXUSRCLK0/1. For a two-byte interface, RXUSRCLK20/1 runs at one-

half RXUSRCLK0/1. For some standards, TXUSRCLK20/1 is identical to

TXUSRCLK20/1.

Notes:

1. 10-bit internal data width is necessary when the RX buffer is bypassed.

Table 7-34: FPGA RX Interface Ports (Continued)

Port Dir Clock Domain Description

Table 7-35: RX Datapath Width Configuration

INTDATAWIDTH

(1,2)

RXDATAWIDTH

(3)

RXDEC8B10BUSE FPGA RX Interface Width

00N/A 8 bits

01N/A 16 bits

10 0 10 bits

10 1 8 bits

11 0 20 bits

11 1 16 bits

Notes:

1. 10-bit internal data width is necessary when the RX buffer is bypassed.

2. The internal datapath is 8 bits when INTDATAWIDTH = 0 and 10 bits when INTDATAWIDTH = 1.

3. The RXDATA interface is one byte wide when RXDATAWIDTH = 0 and two bytes wide when

RXDATAWIDTH = 1.

Loading...

Loading...