138 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 7: GTP Receiver (RX)

R

CDR Reset

The CDR must be reset before it can operate on incoming data. There are several ways to

reset the CDR:

• Use the GTPRESET port to reset all components in the GTP_DUAL tile, including the

CDR in each transceiver. See “Reset,” page 72 for more details.

• Use the RXCDRRESET port to reset the CDR block, the OOB circuits for SATA (see

“RX OOB/Beacon Signaling,” page 129), the RX buffer (see “Configurable RX Elastic

Buffer and Phase Alignment,” page 161), and the remaining sections of the RX PCS.

• Use the RXELECIDLERESET and RXENELECIDLERESETB ports, which are part of

the Link Idle Reset described in “Reset,” page 72. The Link Idle Reset circuit must be

implemented whenever a GTP receiver is used. The RXENELECIDLERESET port

enables the RXELECIDLE RESET port, which is used to reset the CDR without

resetting any other blocks in response to electrical idle conditions.

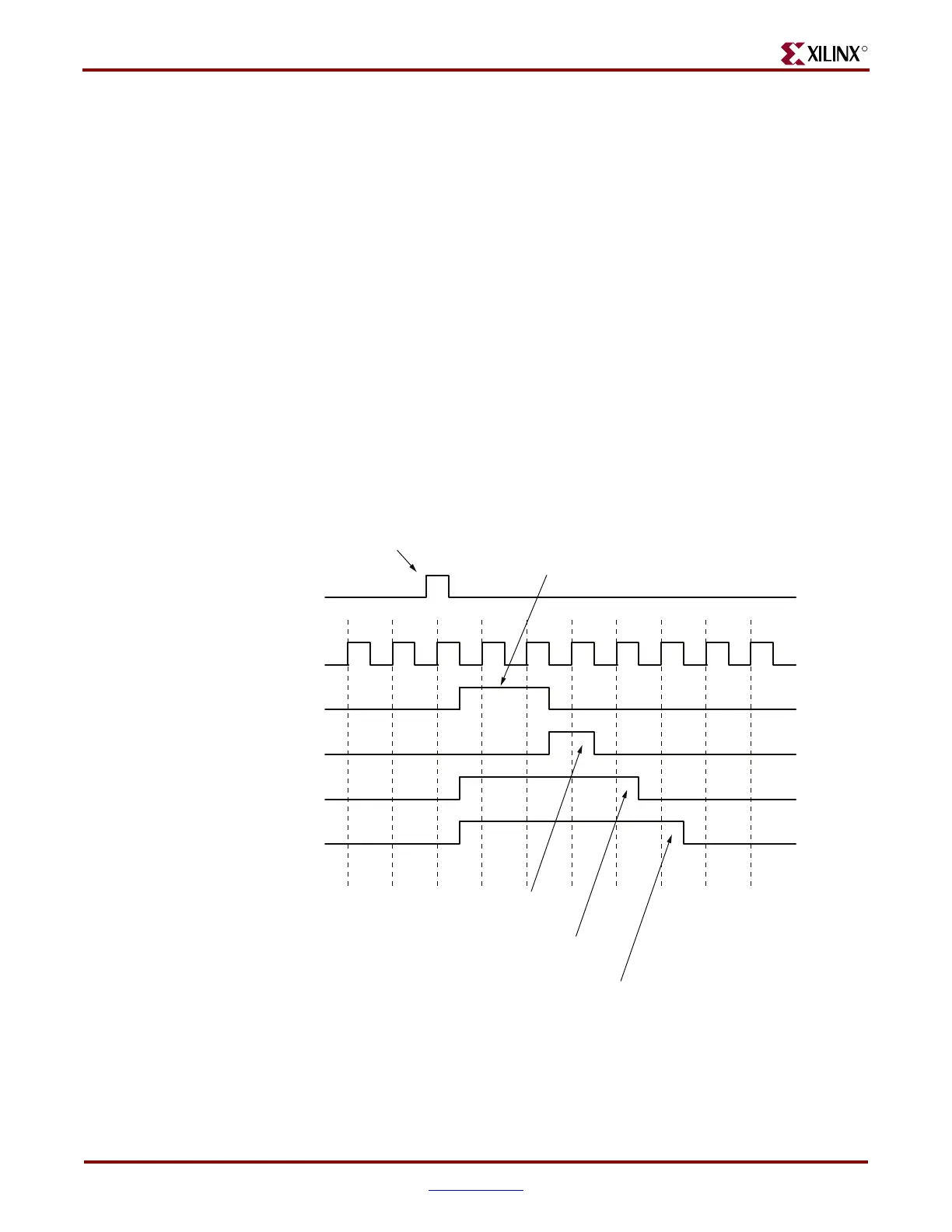

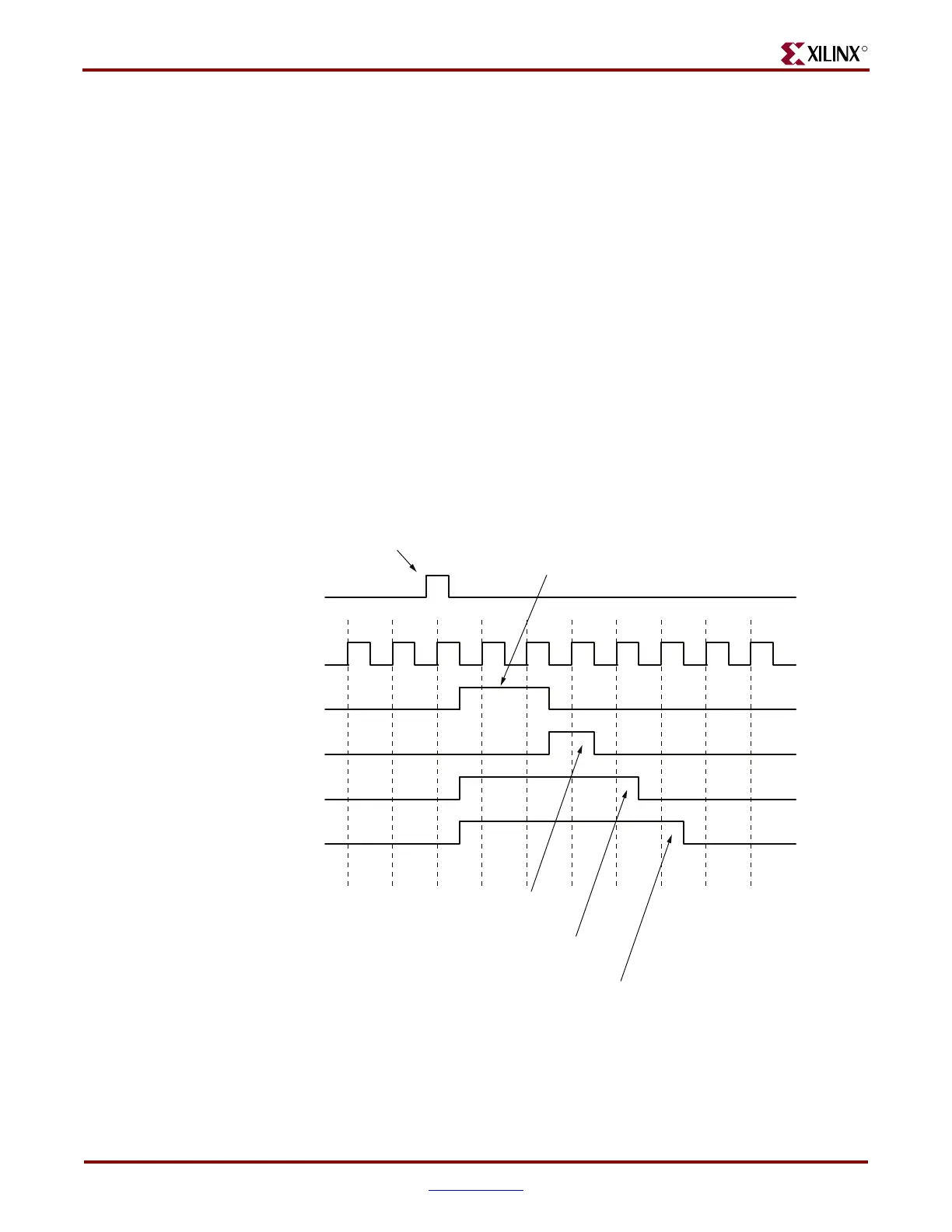

Figure 7-5 shows the timing of the internal reset signals when RXCDRRESET is asserted.

RXCDRRESET can be asserted asynchronously. When it is asserted, an internal CDR reset

pulse, synchronized to an internally generated 1 MHz clock, resets the CDR. Similarly, a

reset pulse is generated for the SATA OOB circuit (internal SATA reset), the RX PCS

datapath (internal RXRESET), and the RX buffer (internal RXBUFRESET). The entire

sequence completes in approximately 5 µs.

Figure 7-5: Reset Sequence Triggered by RXCDRRESET

RXCDRRESET

Internal CDR Reset

Internal SATA Reset

Internal RXRESET

Internal RXBUFRESET

Asynchronous Pulse

Internal 1 MHz Clock

High for at least 2 μs

High for 1 μs

Deasserts 1 μs later

Deasserts 1 μs later

Total Reset time ~ 5 μs

UG196_c7_05_080806

Loading...

Loading...