164 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 7: GTP Receiver (RX)

R

The RX buffer can also be used when OVERSAMPLE_MODE is TRUE.

To use the RX buffer to resolve phase differences between the domains:

• Set RX_BUFFER_USE to TRUE.

• Reset the buffer whenever RXBUFSTATUS indicates an overflow or an underflow.

• The buffer can be reset using GTPRESET (see “Reset,” page 72), RXRESET, or

RXBUFRESET.

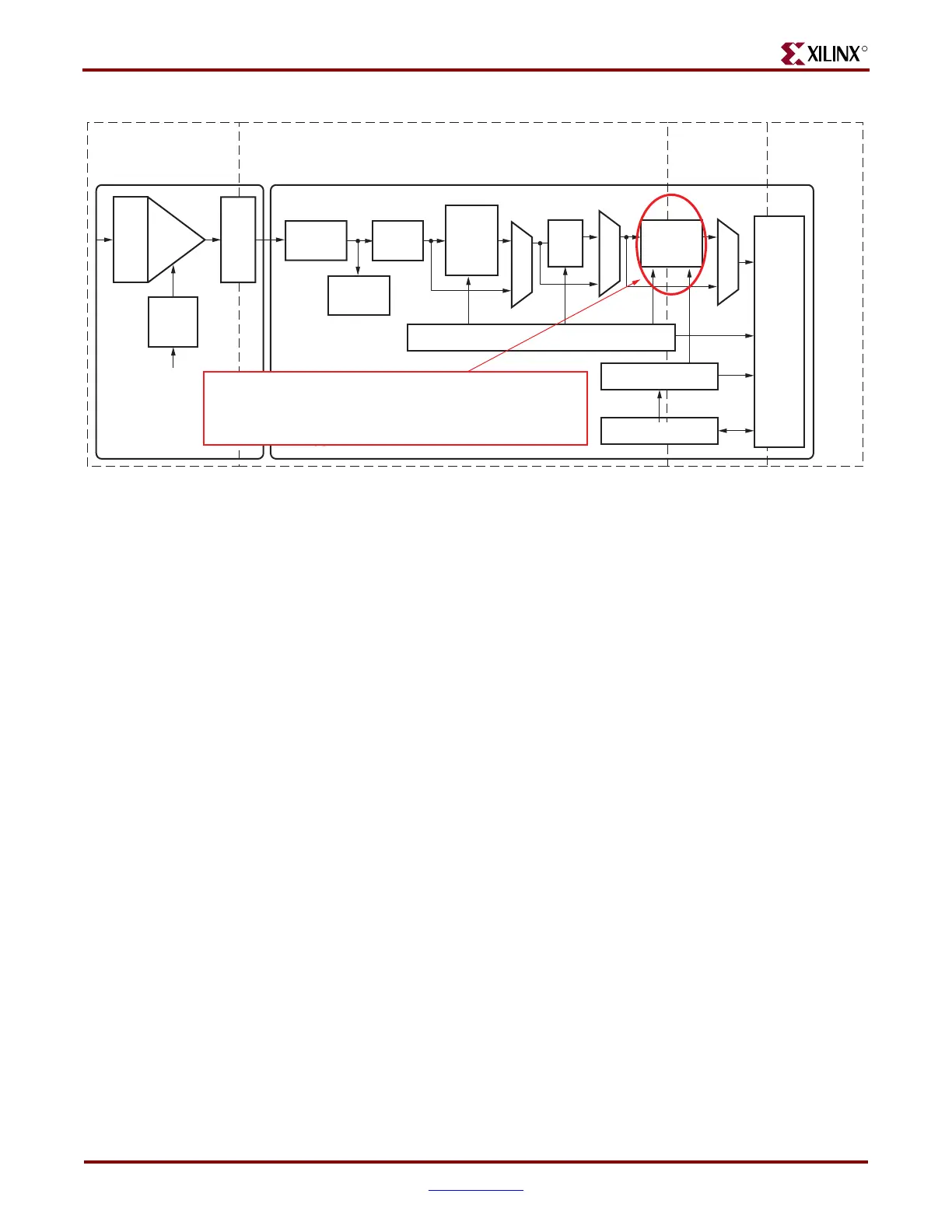

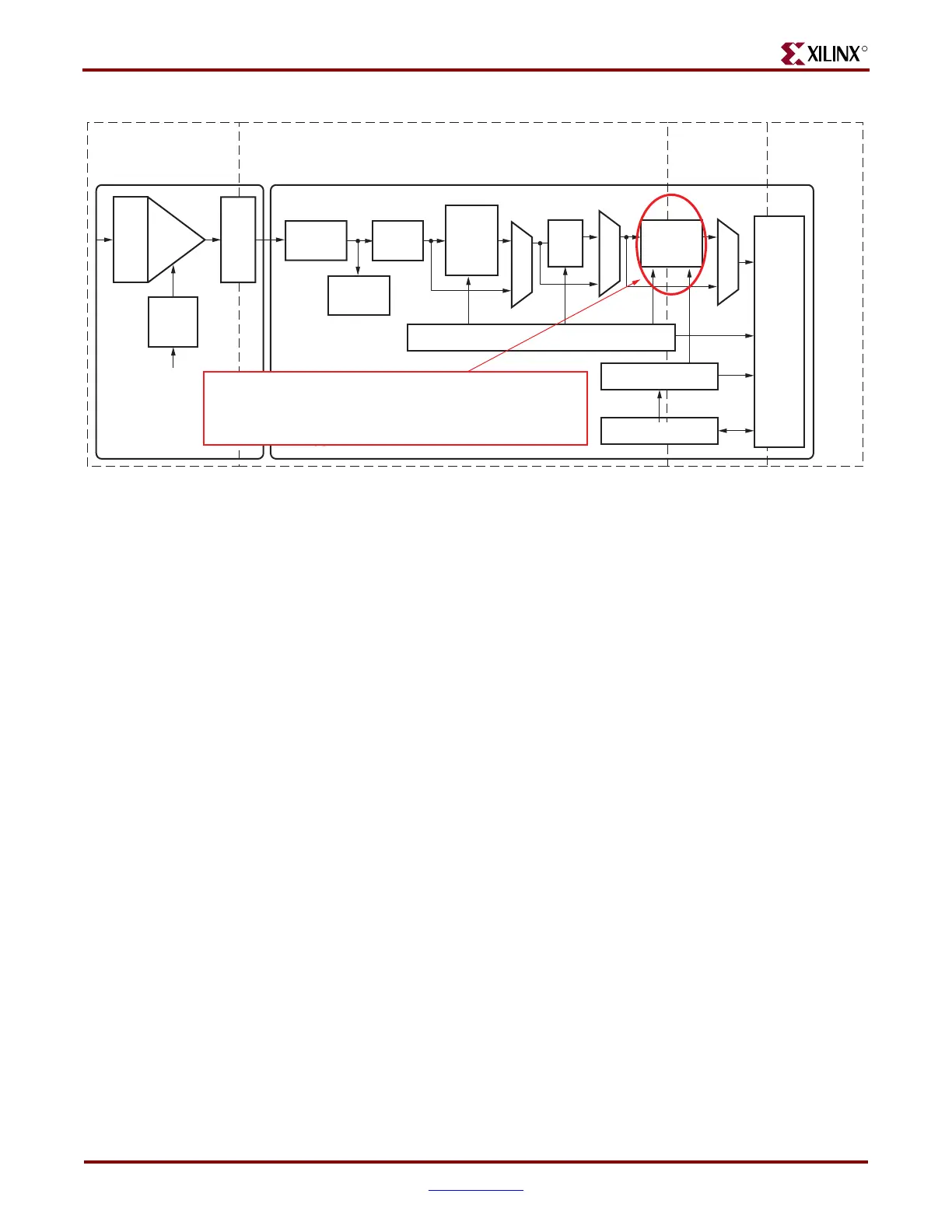

Using RX Phase Alignment

The RX buffer can be bypassed to reduce latency when INTDATAWIDTH = 1 (10-bit

internal datapath width) and RXRECCLK is used to source RXUSRCLK and RXUSRCLK2.

When the RX buffer is bypassed, latency through the RX datapath is low and deterministic,

but clock correction and channel bonding are not available.

Figure 7-22 shows how phase alignment allows the RX buffer to be bypassed. Before phase

alignment, there is no guaranteed phase relationship between the parallel clock from the

SIPO (XCLK) and the parallel clocks from the FPGA logic (RXUSRCLK and RXUSRCLK2).

Phase alignment causes RXRECCLK from the SIPO to be adjusted so that there is no

significant phase difference between XCLK and RXUSRCLK.

Figure 7-21: Using the RX Buffer

RX Serial Clock

RX-PMA RX-PCS

RX

CDR

PMA

PLL

Divider

From PMA PLL

RX

EQ

SIPO

FPGA

Logic

Elastic

Buffer

RX Status Control

10B

/

8B

Loss of Sync

Over-

Sampling

PMA Parallel Clock

(XCLK)

PCS Parallel

Clock

(RXUSRCLK)

RX Interface

Parallel Clock

(RXUSRCLK2)

Polarity

PRBS

Check

RX Pipe Control

Comma

Detect

&

Align

UG196_c7_21_102306

- Resolves phase differences between XCLK and RXUSRCLK

- Resolves frequency differences between XCLK and RXUSRCLK

(requires clock correction)

- Removes RX skew between lanes (requires channel bonding)

Loading...

Loading...