Virtex-5 RocketIO GTP Transceiver User Guide www.xilinx.com 165

UG196 (v1.3) May 25, 2007

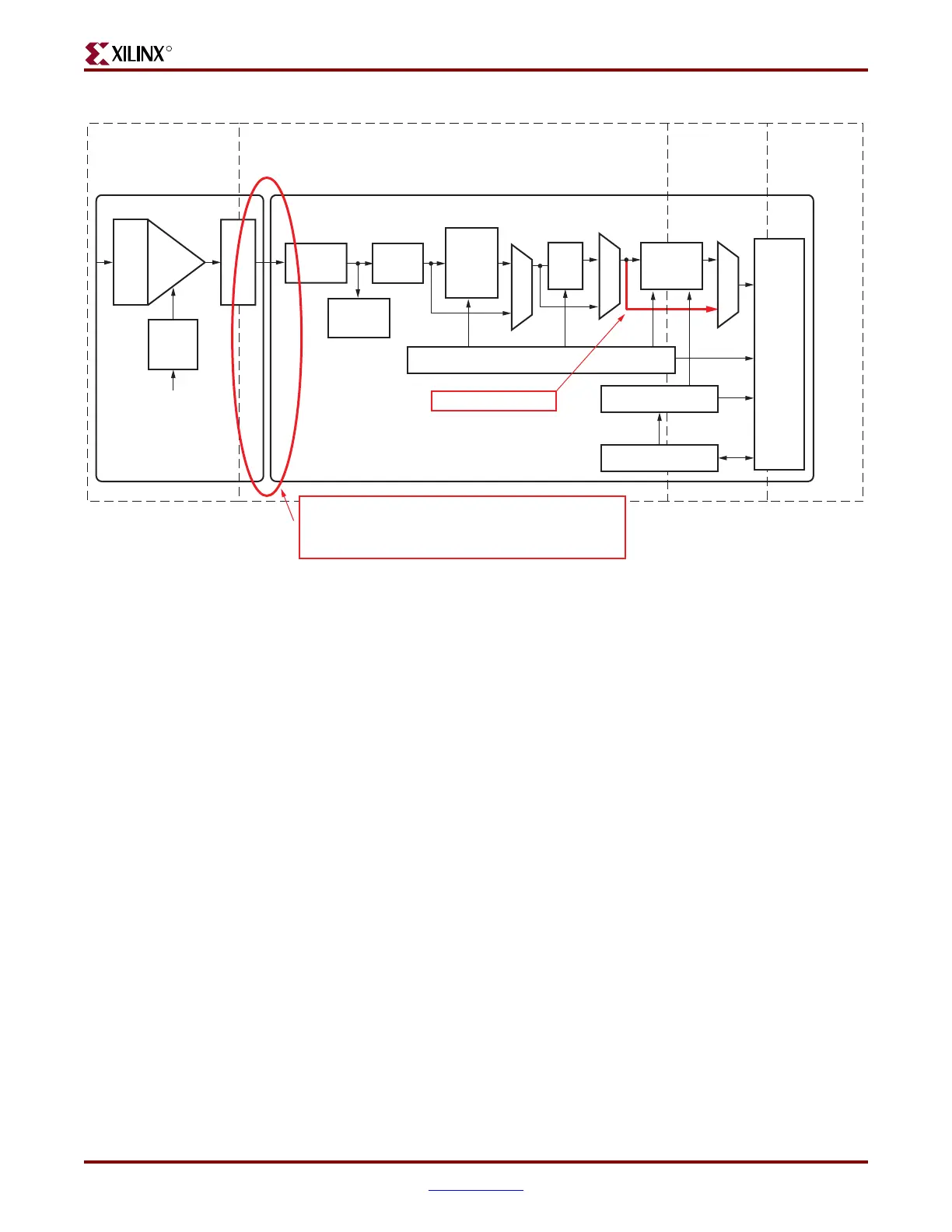

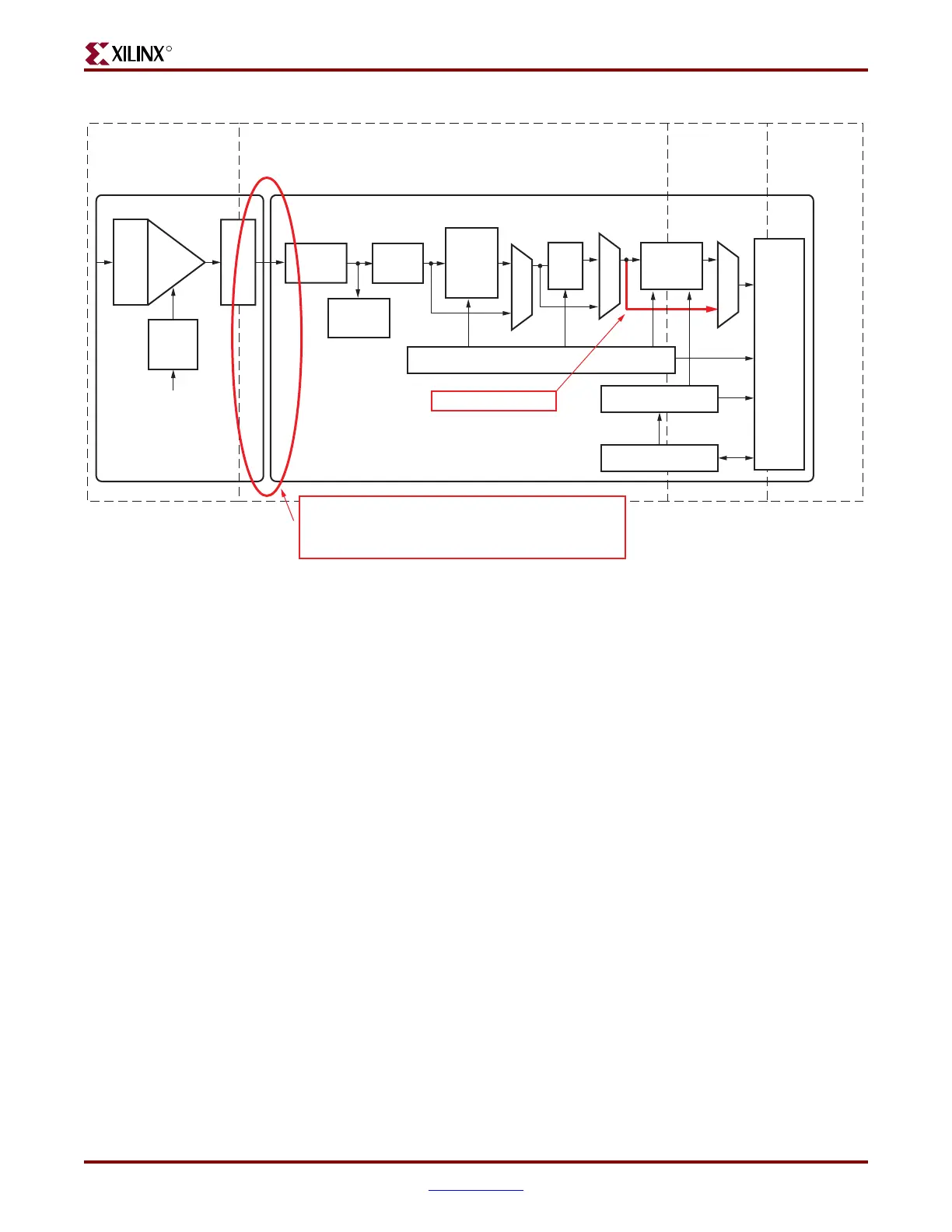

Configurable RX Elastic Buffer and Phase Alignment

R

Phase alignment can only be used for 10-bit internal datapaths (INTDATAWIDTH = 1).

To use RX phase alignment:

1. Set RX_BUFFER_USE to FALSE to bypass the RX buffer (optional).

2. Set RX_XCLK_SEL to RXUSR.

3. Source RXUSRCLK and RXUSRCLK2 with the RXRECCLK output. Divide

RXRECCLK by 2 if necessary to provide RXUSRCLK2 (see “FPGA RX Interface,” page

182 for details).

4. Reset the RX datapath using GTPRESET or one of the CDR resets.

5. Wait for the Shared PMA PLL and any DCM or PLL used for RXUSRCLK2 to lock.

6. Wait for the CDR to lock and provide a stable RXRECCLK.

7. Drive RXPMASETPHASE High for 32 RXUSRCLK2 cycles and then deassert it.

Step 6 requires careful consideration. Normally CDR lock is detected by measuring the

quality of incoming data. Methods for detecting CDR lock include:

• Finding known data in the incoming datastream (for example, commas or A1/A2

framing characters). In general, several consecutive known data patterns should be

received without error to indicate a CDR lock.

• Using the Loss of Sync State Machine (see “Configurable Loss-of-Sync State

Machine,” page 155). If incoming data is 8B/10B encoded and the CDR is locked, the

LOS state machine should move to the SYNC_ACQUIRED state and stay there.

When the RX buffer is bypassed, data received from the PMA might be distorted due to

phase differences as it passes to the PCS. This makes it difficult to determine whether bad

Figure 7-22: Using Phase Alignment

RX Serial Clock

RX-PMA RX-PCS

RX

CDR

PMA

PLL

Divider

From PMA PLL

RX

EQ

SIPO

FPGA

Logic

Elastic

Buffer

RX Status Control

10B

/

8B

Loss of Sync

Over-

Sampling

PMA Parallel Clock

(XCLK)

PCS Parallel

Clock

(RXUSRCLK)

RX Interface

Parallel Clock

(RXUSRCLK2)

Polarity

PRBS

Check

RX Pipe Control

RX Buffer Bypassed

Comma

Detect

&

Align

UG196_c7_33_102306

After phase alignment:

- SIPO parallel clock phase matches RXUSRCLK phase

- No phase difference between XCLK and RXUSRCLK

Loading...

Loading...