168 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 7: GTP Receiver (RX)

R

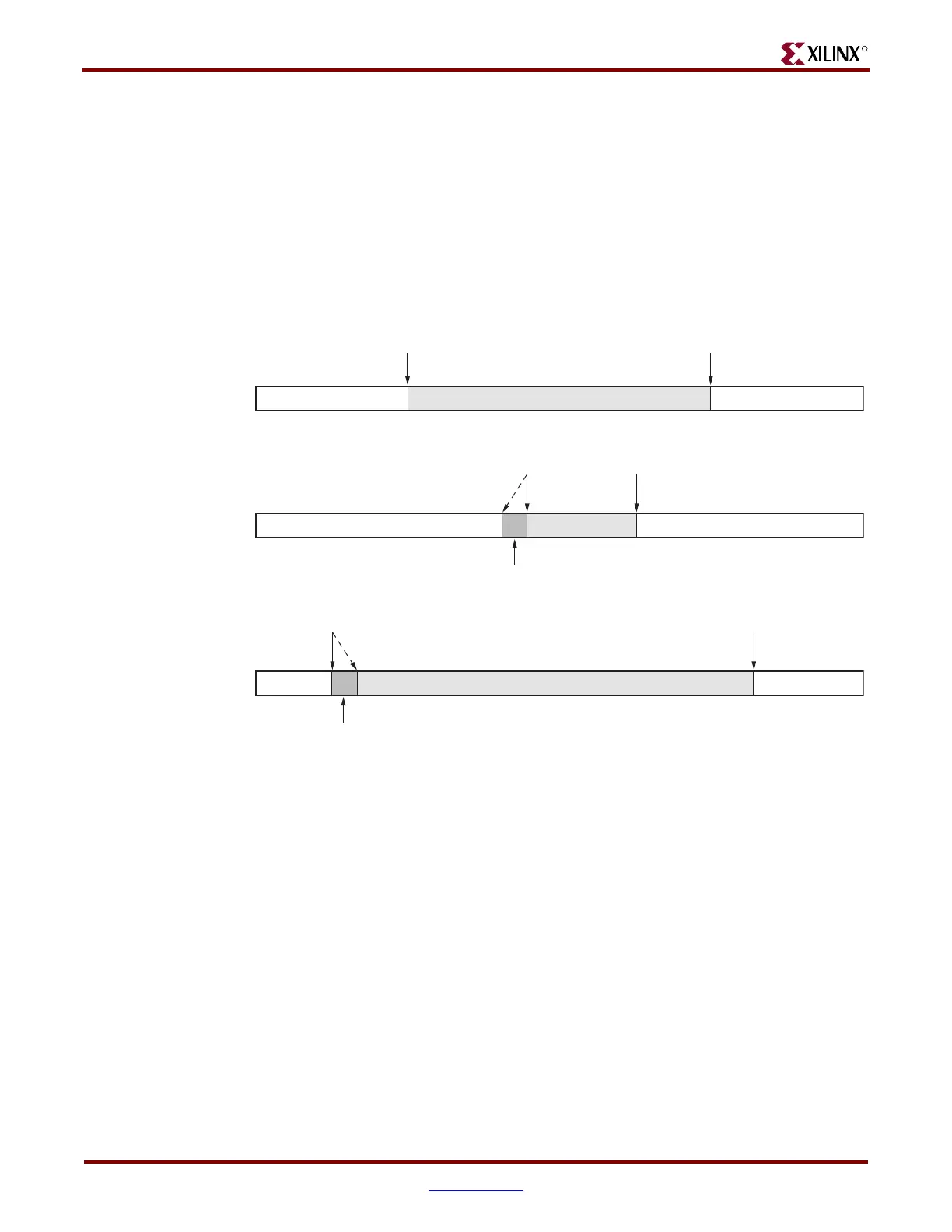

Configurable Clock Correction

Overview

The RX elastic buffer has an additional benefit: it can tolerate frequency differences

between the XCLK and RXUSRCLK domains by performing clock correction. Clock

correction actively prevents the RX elastic buffer from getting too full or too empty by

deleting or replicating special idle characters in the data stream.

Figure 7-25 shows a conceptual view of clock correction.

Clock correction should be used whenever there is a frequency difference between XCLK

and RXUSRCLK. It can be avoided by using the same frequency source for TX and RX, or

by using the recovered clock to drive RXUSRCLK. The “Configurable RX Elastic Buffer

and Phase Alignment” section has more details about the steps required if clock correction

is not used.

Figure 7-25: Clock Correction

Write

XCLK

“Nominal” Condition: Buffer Half Full

Buffer Less Than Half Full (Emptying)

Buffer More Than Half Full (Filling Up)

Read

RXUSRCLK

WriteRead

Repeatable Sequence

Write

UG196_c7_22_092606

Repeatable Sequence

Read

Loading...

Loading...