Virtex-5 RocketIO GTP Transceiver User Guide www.xilinx.com 311

UG196 (v1.3) May 25, 2007

GTP Receiver Latency

R

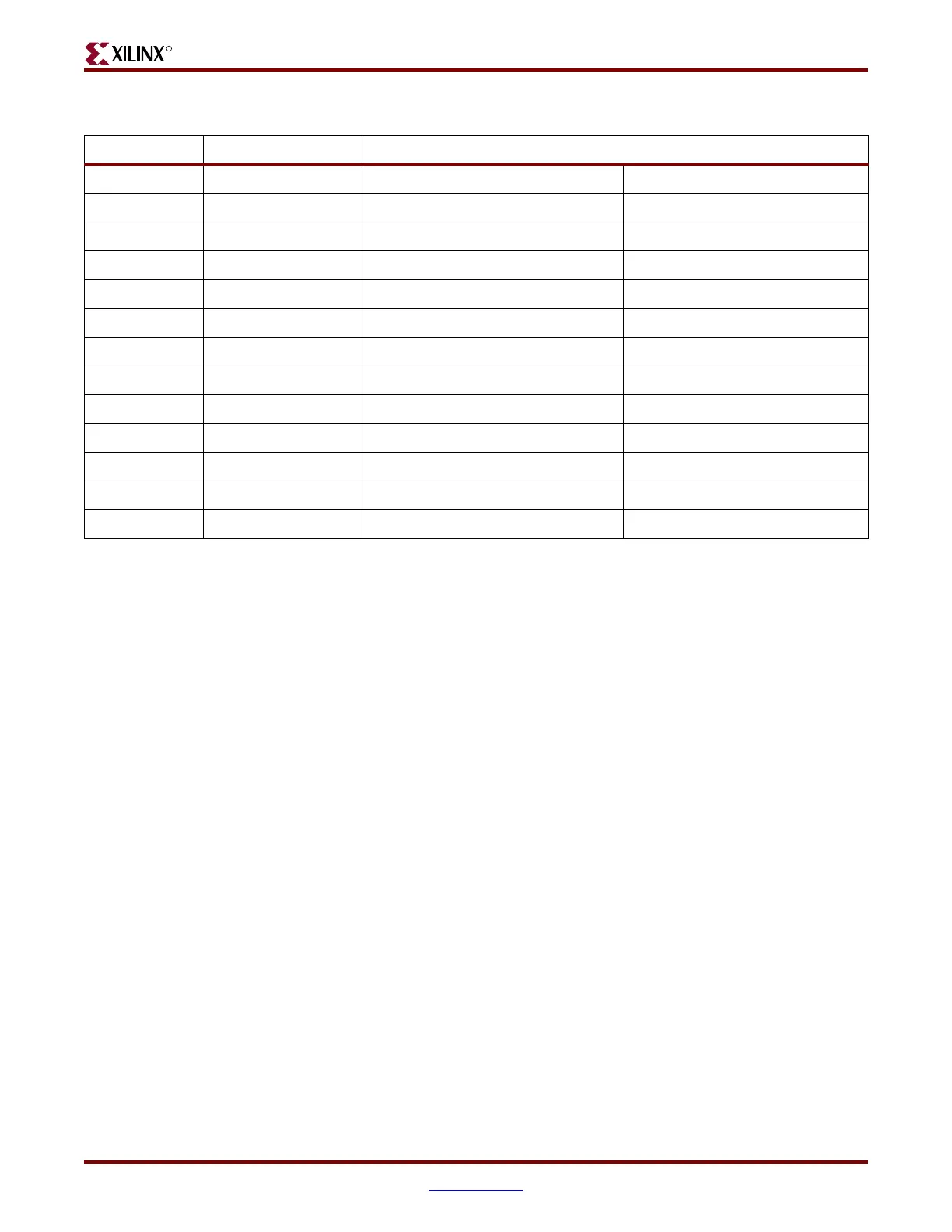

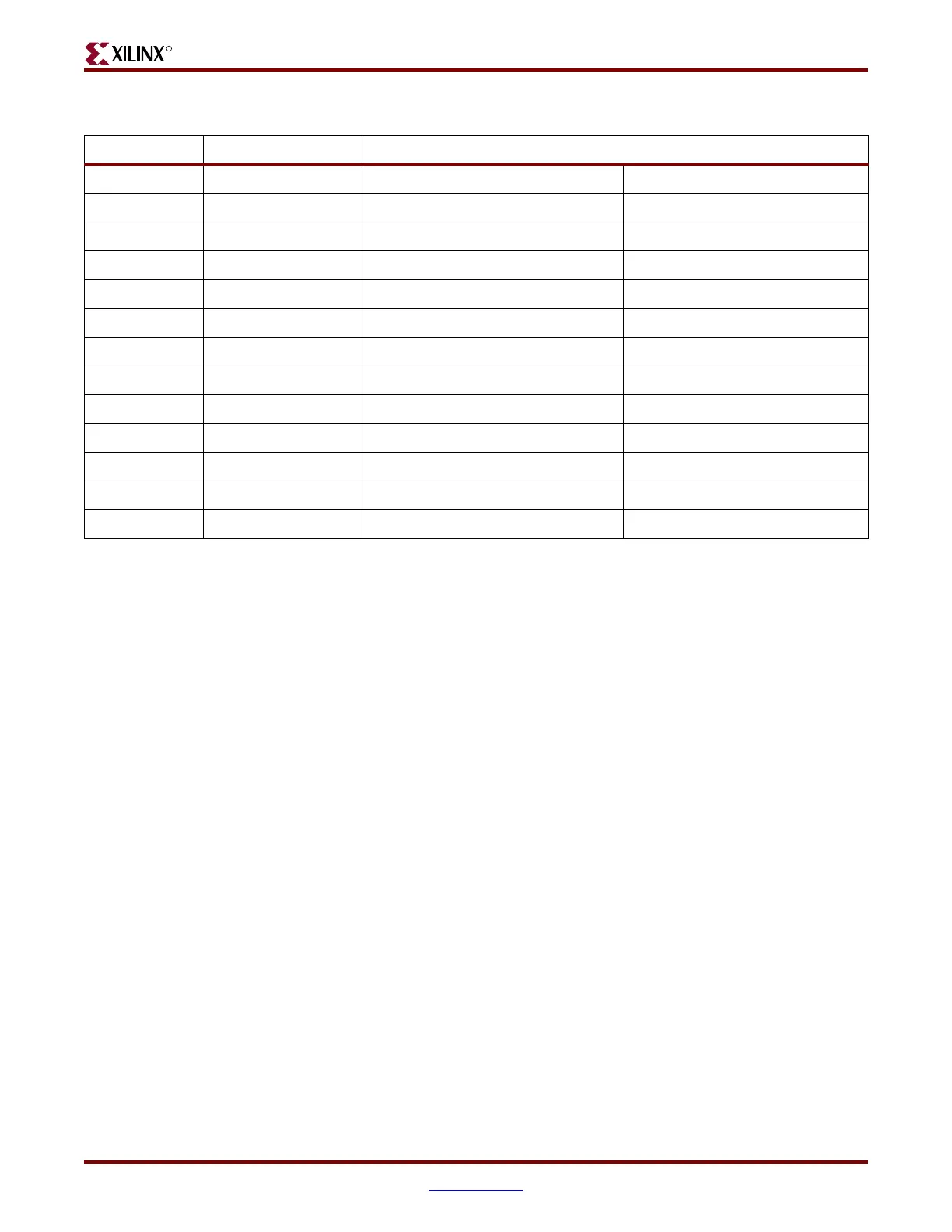

Table E-2: GTP Receiver Latency

Block Number Block Name Latency

RXDATAWIDTH = 0 RXDATAWIDTH = 1

14 Fabric Interface 2 cycles 3 cycles

RXDEC8B10BUSE = 0

(2)

RXDEC8B10BUSE = 1

10 8B/10B Encoder 0 cycles 1 cycle

RX_BUFFER_USE = 0 RX_BUFFER_USE = 1

11 RX FIFO 2 cycles 2 cycles + CLK_COR_MIN_LAT

RXCOMMADETUSE = 0 RXCOMMADETUSE = 1

8 Comma Alignment 2 cycles 2-4 cycles

OVERSAMPLE_MODE = FALSE OVERSAMPLE_MODE = TRUE

5+6 Oversampling 1 cycle

1+2+3+4 PMA + Interface 1.5 ± 1 cycle

Total Latency Max Min

Not oversampling 13.5 + CLK_COR_MIN_LAT 7.5 cycles

Notes:

1. 1 cycle = 1 clock cycle at the RXUSRCLK rate.

2. When the RX buffer is bypassed, 10-bit internal data width is necessary, therefore, INTDATAWIDTH = 1.

Loading...

Loading...