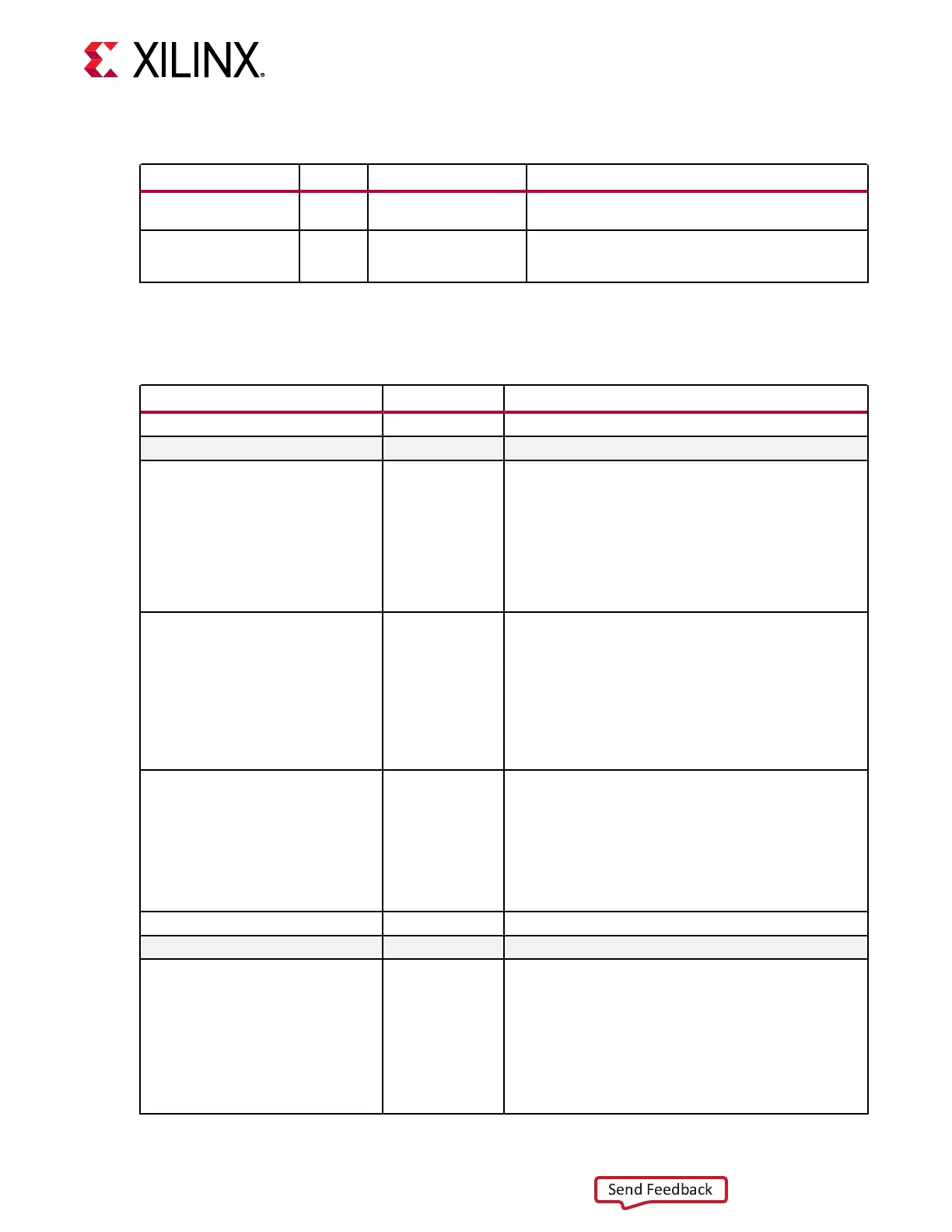

Table 71: RX Interface Ports (cont'd)

Port Dir Clock Domain Description

RXUSRCLK In Clock This port is used to provide a clock for the internal RX

PCS datapath.

RXUSRCLK2 In Clock This port is used to synchronize the interconnect logic

with the RX interface. This clock must be positive-edge

aligned to RXUSRCLK.

The following table denes the TX interface aributes.

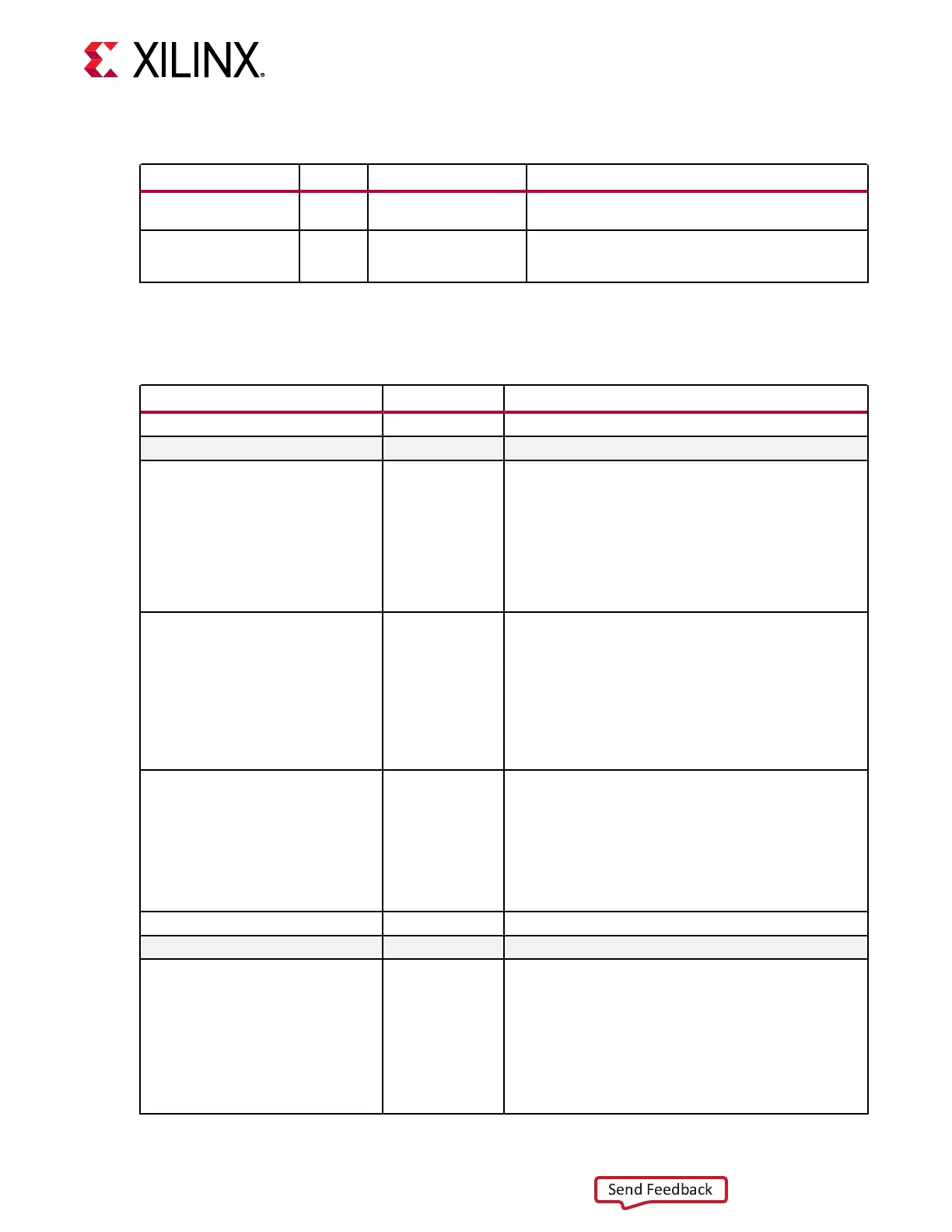

Table 72: RX Interface Attributes

Attribute Type Description

CH[0/1]_RX_PCS_CFG0 16-bit Reserved.

Bit Name Address Description

RX_DATA_WIDTH [2:0] Sets the bit width of the RXDATA port. When FEC is enabled,

RX_DATA_WIDTH must be set to 160:

0x0: 64-bit fabric mode.

0x1: 80-bit fabric mode.

0x2: 128-bit fabric mode.

0x3: 160-bit fabric mode.

0x4: 256-bit fabric mode.

RX_INT_DATA_WIDTH

[4:3] Controls the width of the internal RX PCS datapath. 80-bit

internal datapath must use with 80- or 160-bit fabric width;

128-bit internal datapath must use with 128- or 256-bit

fabric width; 64-bit internal datapath must use with 64 or

128-bit fabric width:

0x0: 64-bit internal datapath mode.

0x1: 80-bit internal datapath mode.

0x2: 128-bit internal datapath mode.

GEN_RXUSRCLK

[14] Automatically generates RXUSRCLK from RXUSRCLK2, only

applicable when fabric datapath width is the same as the

internal datapath width:

0x0: Disables automatic RXUSRCLK generation from

RXUSRCLK2.

0x1: Enables automatic RXUSRCLK generation from

RXUSRCLK2.

CH[0/1]_A_CH_CFG0

16-bit Reserved.

Bit Name Address Description

RX_FABINT_USRCLK_FLOP [1] Determines if port signals are registered again in the

RXUSRCLK domain after being registered in the RXUSRCLK2

domain. This attribute only applies if the RX internal

datapath width is the same as the RX interface width,

otherwise this attribute is ignored. Use the recommended

value from the Wizard.

0x0: Bypass RXUSRCLK flip-flops.

0x1: Enable RXUSRCLK flip-flops.

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 116

Loading...

Loading...