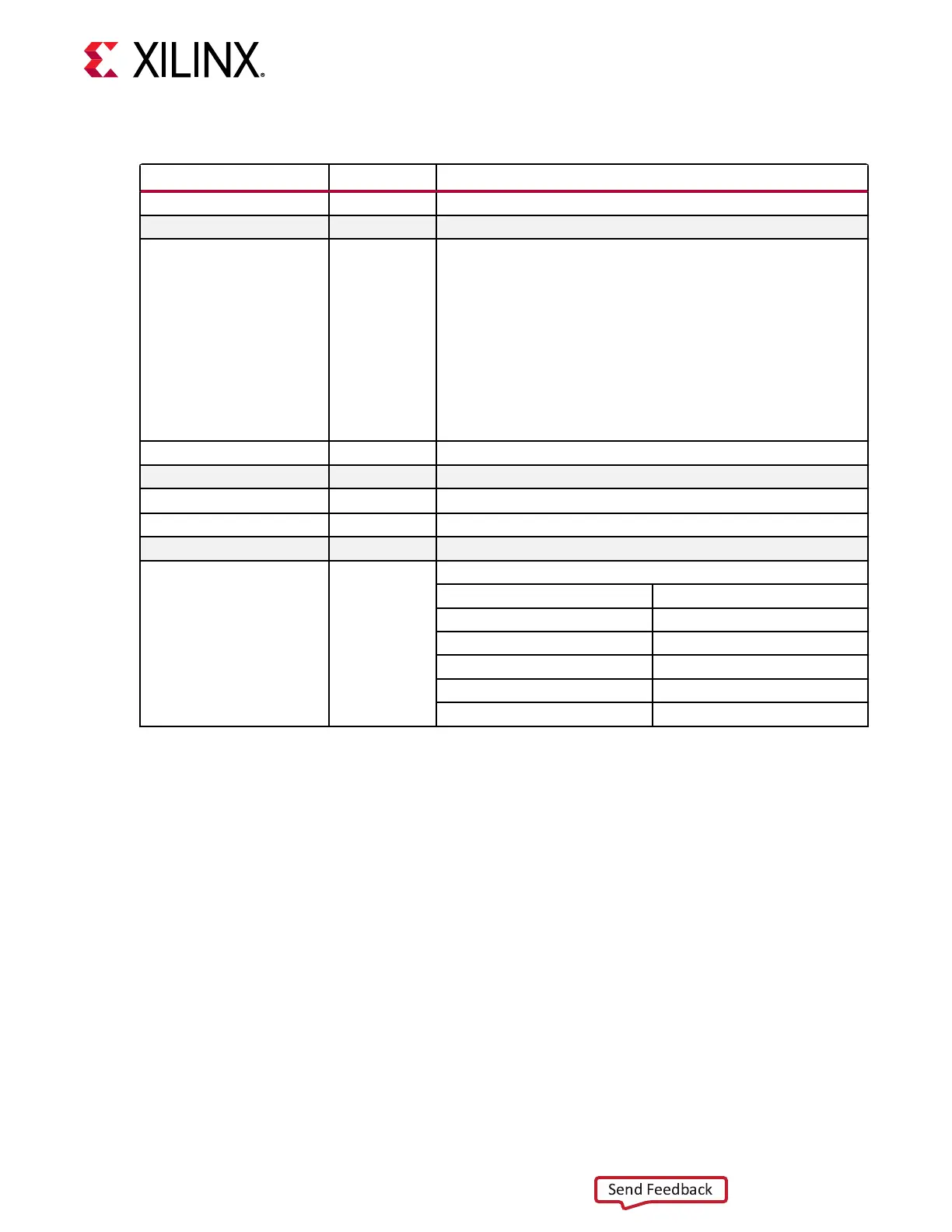

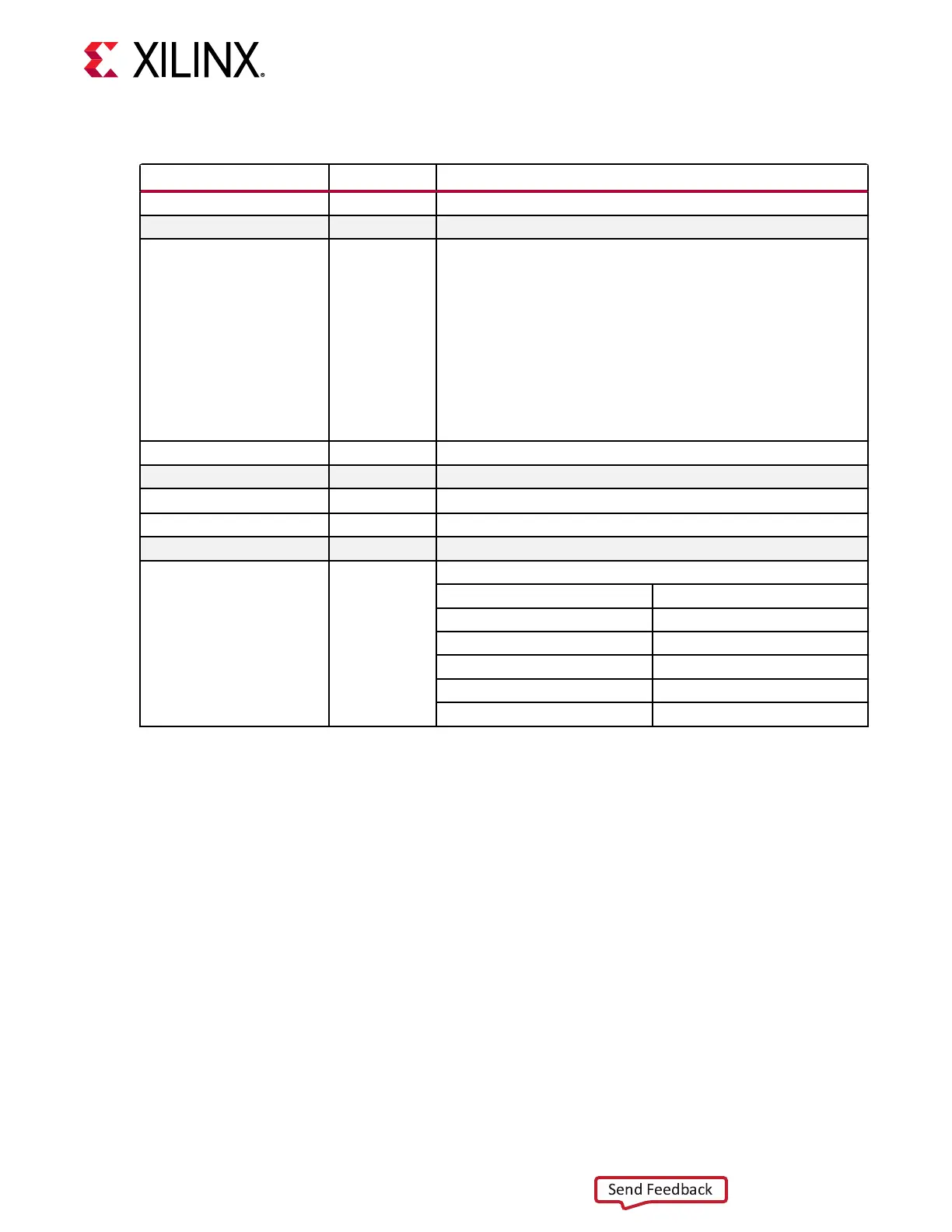

Table 27: Digital Monitor Attributes (cont'd)

Attribute Type Description

CH[0/1]_RX_APT_CFG8B 16-bit Reserved.

Bit Name Bit Field Description

DEMONCON [14:12] Selector for DMON data for channel 0/1.

3’b000: Reserved.

3’b001: Reserved.

3’b010: Reserved.

3’b011: Choose FFE data through FFELOOPSEL.

3’b100: Choose DFE data through DFELOOPSEL.

3’b101: Reserved.

3’b110: Reserved.

3’b111: Reserved.

CH[0/1]_RX_APT_CFG12B

16-bit Reserved.

Bit Name Bit Field Description

TESTSEL [15] Must be set to 1’b0 when reading adaptation loops in channel 0/1.

CH[0/1]_RX_APT_CFG18A 16-bit Reserved.

Bit Name Bit Field Description

DFELOOPSEL [15:12] Selector to monitor DFE and CTLE adaptation loops for channel 0/1.

Value Adaptation Loop

4’b0100

DFE Tap 1.

4’b0110

AGC frequency gain.

4’b0111

Low frequency gain.

4’b1000

High frequency gain.

4’b1001

Base line wander cancellation.

Chapter 2: Shared Features

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 51

Loading...

Loading...