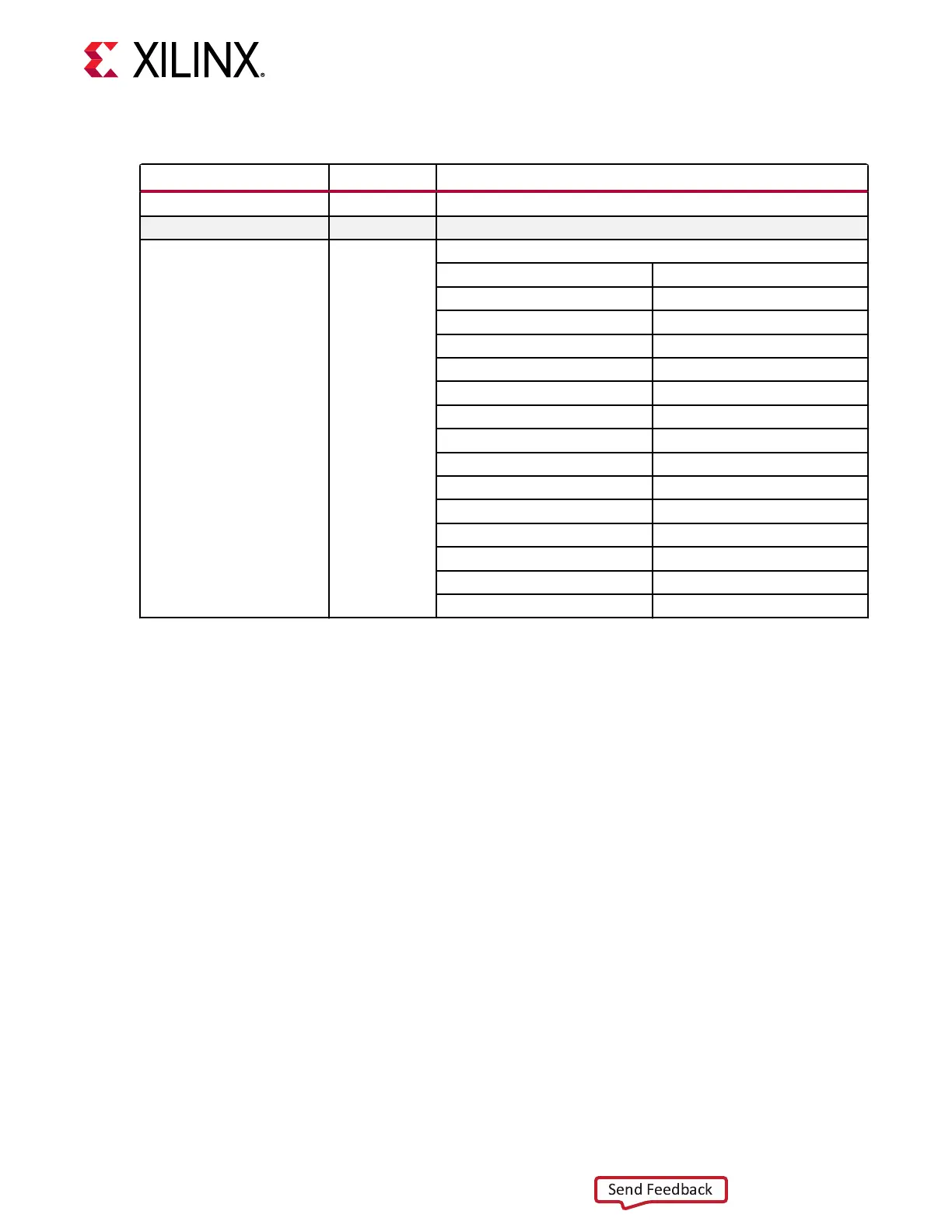

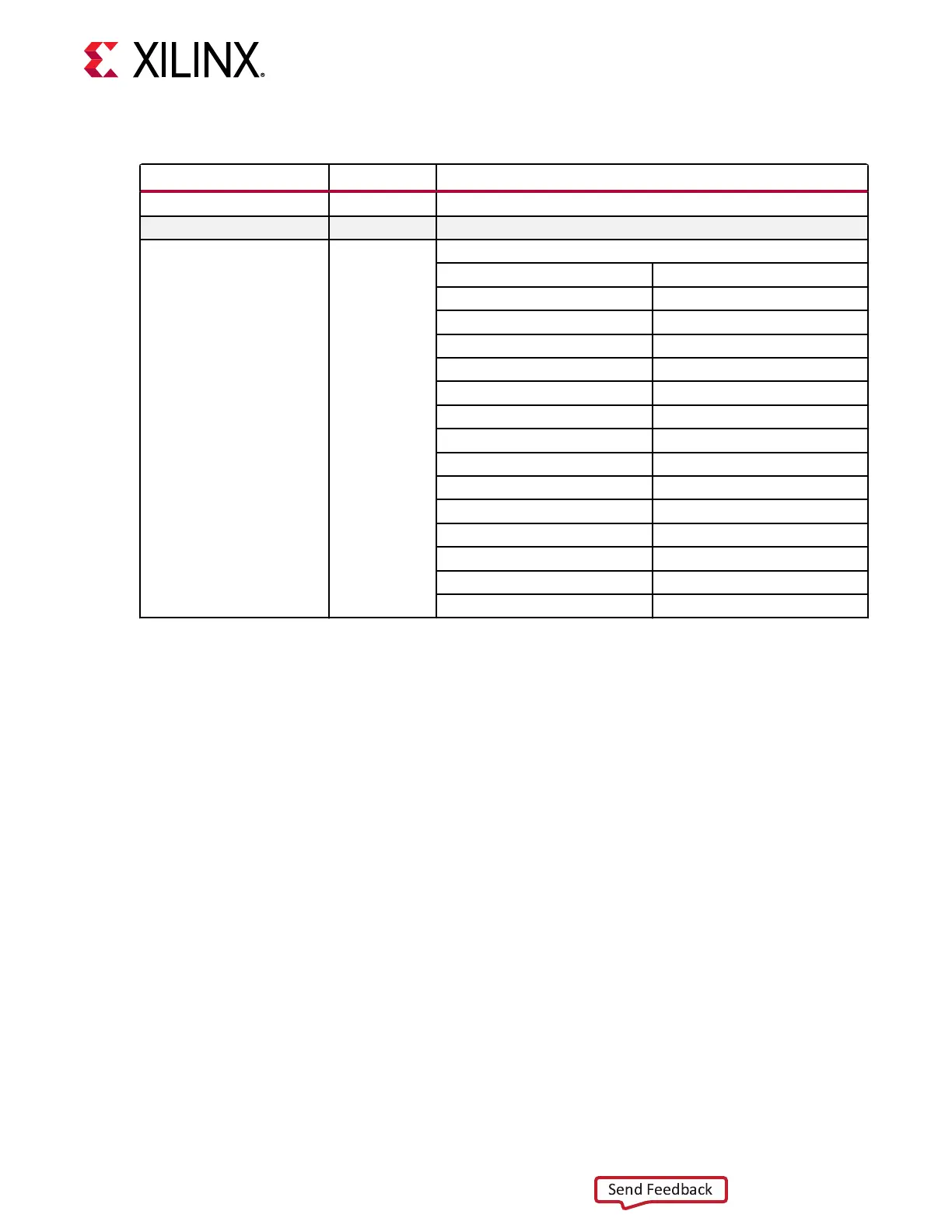

Table 27: Digital Monitor Attributes (cont'd)

Attribute Type Description

CH[0/1]_RX_APT_CFG14B 16-bit Reserved.

Bit Name Bit Field Description

FFELOOPSEL [15:12] Selector to monitor FFE adaptation loops for channel 0/1.

Value Adaptation Loop

4’b0001

FFE tap hm01.

4’b0010

FFE tap hm02.

4’b0011

FFE tap hm03.

4’b0100

FFE tap hm04.

4’b0101

FFE tap hp02.

4’b0110

FFE tap hp03.

4’b0111

FFE tap hp04.

4’b1000

FFE tap hp05.

4’b1001

FFE tap hp06.

4’b1010

FFE tap hp07.

4’b1011

FFE tap hp08.

4’b1100

FFE tap hp09.

4’b1101

FFE tap hp10.

4’b1110

FFE tap hp11.

Use Mode

Reading loop values out of Digital Monitor requires a clock on input port

CH0/1_DMONITORCLK, change adaptaon loop select through DRP, and monitor output

CH0/1_DMONITOROUT. Set aributes DMON_ENABLE, DMON_SRC, DEMONCON, TESTSEL,

and DFELOOPSEL, or FFELOOPSEL via DRP port to enable the digital monitor and select the

appropriate loop for monitoring. The DRP locaons of the aributes are follows.

Channel 0:

• 0x082[0]: DMON_ENABLE

• 0x082[2:1]: DMON_SRC

• 0x033[14:12]: DEMONCON

• 0x03B[15]: TESTSEL

• 0x046[15:12]: DFELOOPSEL

• 0x03f[15:12]: FFELOOPSEL

Channel 1:

• 0x282[0]: DMON_ENABLE

Chapter 2: Shared Features

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 52

Loading...

Loading...