TPU2000/2000R Modbus/Modbus Plus/ Modbus TCP/IP Automation Guide

140

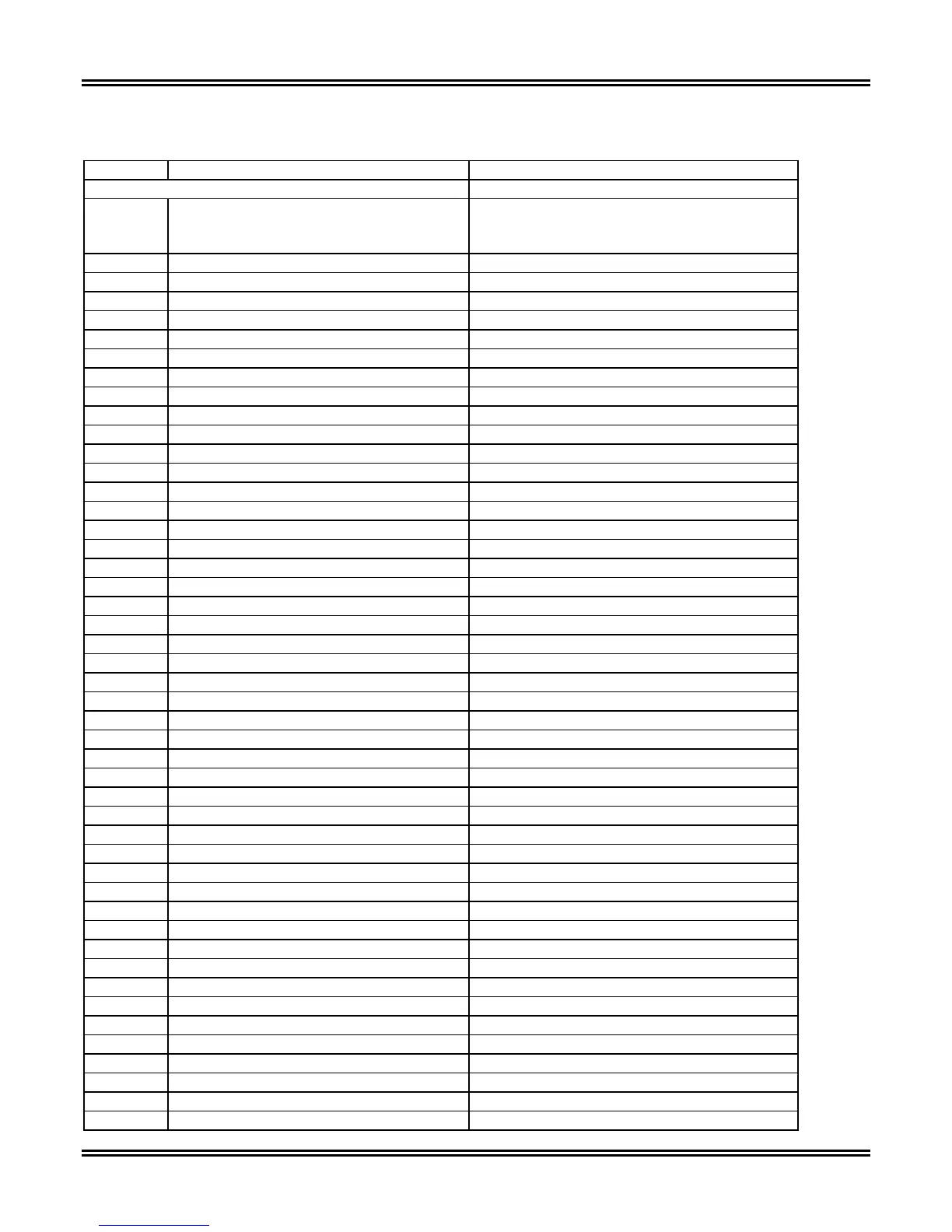

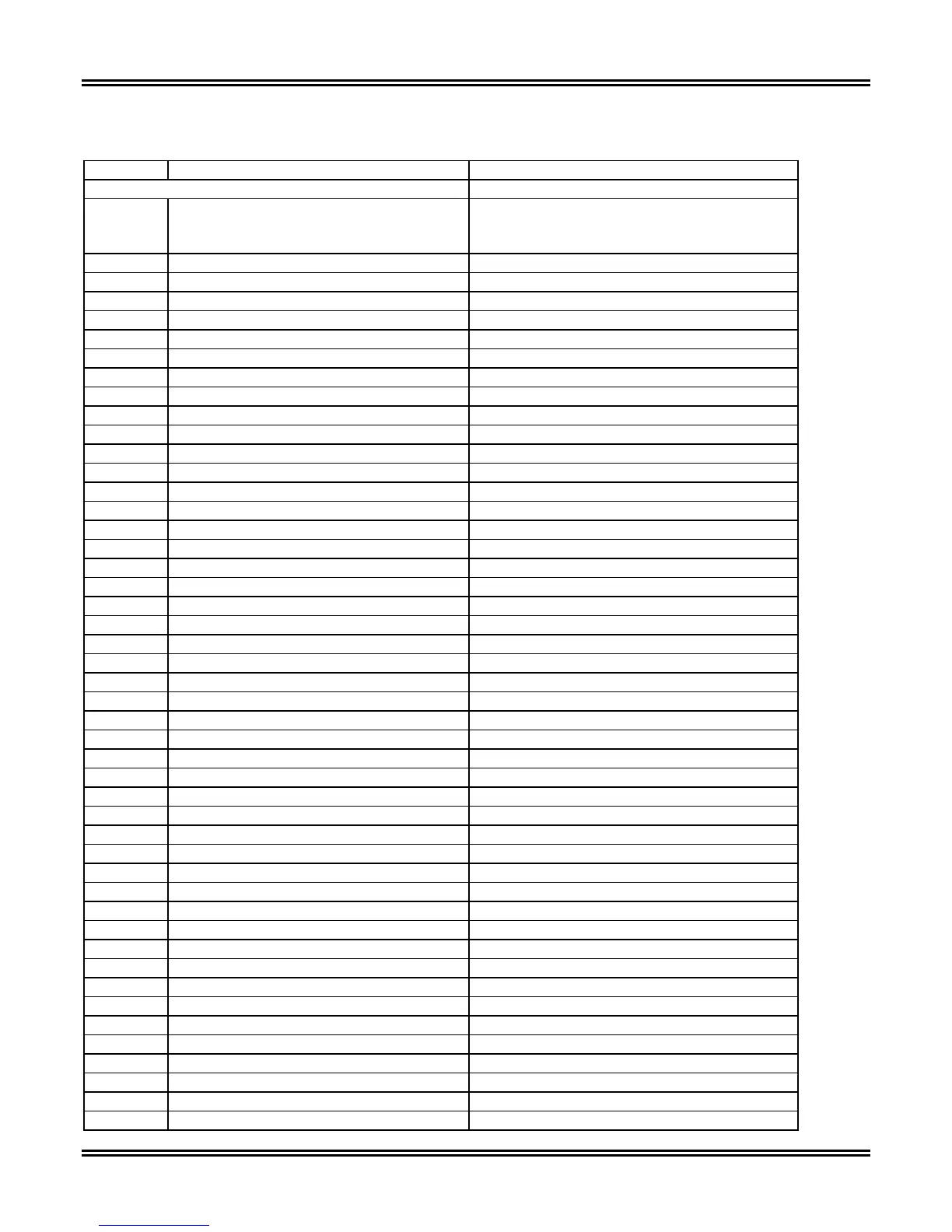

Table 5-43. Group II Bit Definitions for TPU2000R Control

Register Item Description

GROUP II

41416 Execute Register

0 = No Action

1 = Execute

Unsigned (16 Bits)

41417 Password ASCII – 2 Characters Leftmost Digits

41418 Password ASCII – 2 Characters Rightmost Digits

41419 Spare

41420 Force Physical Input Change Mask Unsigned (16 Bits)

Bit 0 Input 1 (Terminal 4) (lsb) 1 = Control Bit State 0 = No Control (lsb)

Bit 1 Input 2 (Terminal 5) 1 = Control Bit State 0 = No Control

Bit 2 Input 3 (Terminal 6) 1 = Control Bit State 0 = No Control

Bit 3 Input 4 (Terminal 7) 1 = Control Bit State 0 = No Control

Bit 4 Input 5 (Terminal 8) 1 = Control Bit State 0 = No Control

Bit 5 Input 6 (Terminal 9) 1 = Control Bit State 0 = No Control

Bit 6 Input 7 (Terminal 10) 1 = Control Bit State 0 = No Control

Bit 7 Input 8 (Terminal 11) 1 = Control Bit State 0 = No Control

Bit 8 Input 9 (Terminal 12) 1 = Control Bit State 0 = No Control

Bit 9 Reserved

Bit 10 Reserved

Bit 11 Reserved

Bit 12 Reserved

Bit 13 Reserved

Bit 14 Reserved

Bit 15 Reserved (msb)

41421 Force Physical Input Normal State Mask Unsigned (16 Bits)

Bit 0 Input 1 (Terminal 4) (lsb) 1 = Normal State Override 0 = Normal State

Bit 1 Input 2 (Terminal 5) 1 = Normal State Override 0 = Normal State

Bit 2 Input 3 (Terminal 6) 1 = Normal State Override 0 = Normal State

Bit 3 Input 4 (Terminal 7) 1 = Normal State Override 0 = Normal State

Bit 4 Input 5 (Terminal 8) 1 = Normal State Override 0 = Normal State

Bit 5 Input 6 (Terminal 9) 1 = Normal State Override 0 = Normal State

Bit 6 Input 7 (Terminal 10) 1 = Normal State Override 0 = Normal State

Bit 7 Input 8 (Terminal 11) 1 = Normal State Override 0 = Normal State

Bit 8 Input 9 (Terminal 12) 1 = Normal State Override 0 = Normal State

Bit 9 Reserved

Bit 10 Reserved

Bit 11 Reserved

Bit 12 Reserved

Bit 13 Reserved

Bit 14 Reserved

Bit 15 Reserved (msb)

41422 Force Physical Input Forcing State Mask Unsigned (16 Bits)

Bit 0 Input 1 (Terminal 4) (lsb) 1 = Force Set State 0 = Force Reset State

Bit 1 Input 2 (Terminal 5) 1 = Force Set State 0 = Force Reset State

Bit 2 Input 3 (Terminal 6) 1 = Force Set State 0 = Force Reset State

Bit 3 Input 4 (Terminal 7) 1 = Force Set State 0 = Force Reset State

Bit 4 Input 5 (Terminal 8) 1 = Force Set State 0 = Force Reset State

Bit 5 Input 6 (Terminal 9) 1 = Force Set State 0 = Force Reset State

Bit 6 Input 7 (Terminal 10) 1 = Force Set State 0 = Force Reset State

Bit 7 Input 8 (Terminal 11) 1 = Force Set State 0 = Force Reset State

Loading...

Loading...