325

Chapter 7 Tutorial

Direct Digital Synthesis

4

7

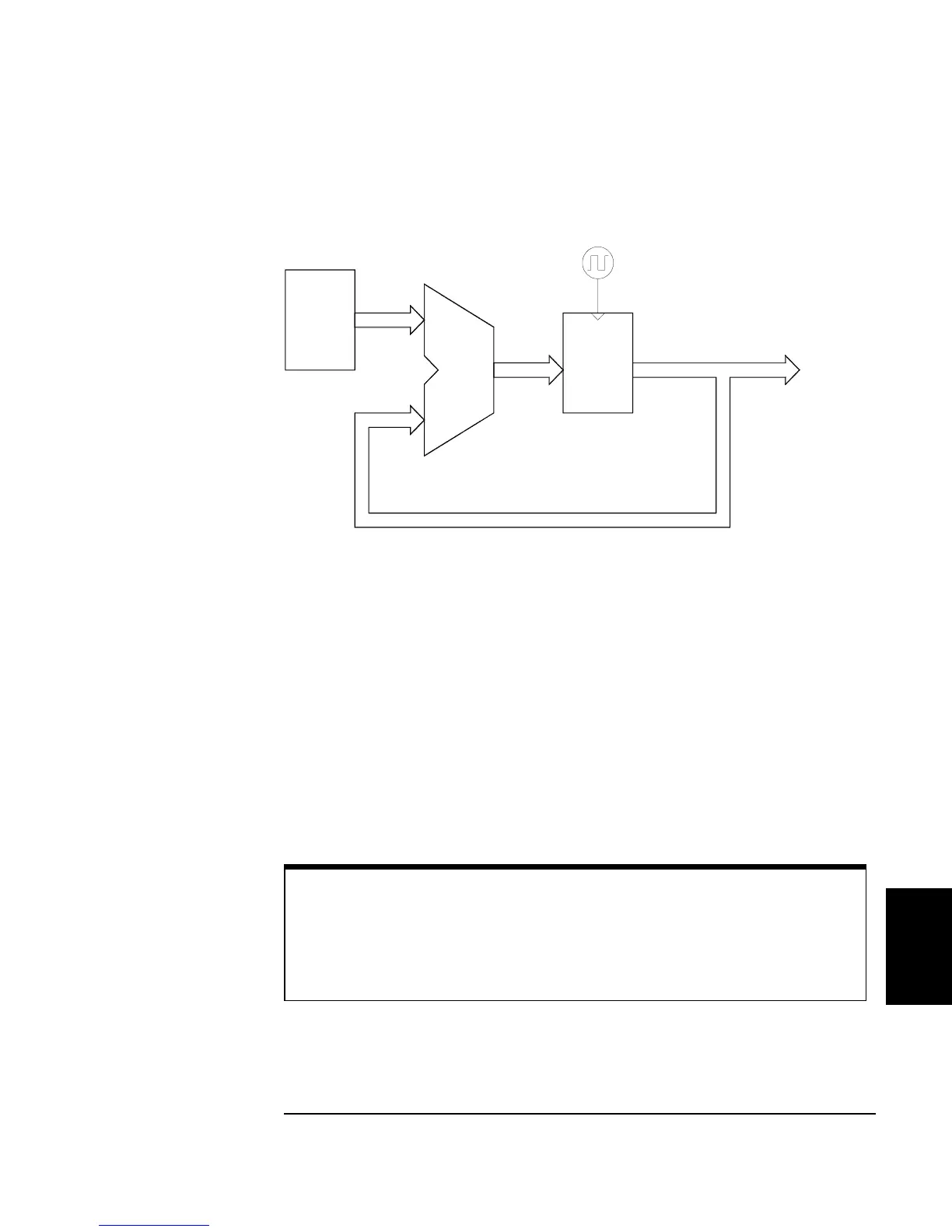

Phase Accumulator Circuitry

The 33220A uses a 64-bit phase accumulator which yields 2

-64

x

50 MHz

or

2.7 picohertz frequency resolution internally. Note that only the 14 or 16

most-significant bits of the Phase Register are used to address waveform

memory. Therefore, when synthesizing low frequencies (less than 3.05

kHz for a typical, 16K point waveform), the address will not change in

every clock cycle. However, at higher frequencies (greater than 3.05

kHz), the address will change by more than one location during each

clock cycle and some points will be skipped. If too many points are

skipped, a phenomenon known as “aliasing” will occur and the waveform

output will become somewhat distorted.

50 MHz

Wavefor

Phase

Adder

64 Bits

Register

egister (PIR)

64 Bits

MSBs

(

14 or 16 bits

)

Memory

Address

ncrement

64 Bits

The Nyquist Sampling Theorem states that in order to prevent aliasing,

the highest frequency component of the desired output waveform must

be

less than half of the sampling frequency. The Agilent 33220A

samples at 50 MHz, so Nyquist limits the highest frequency component

to 25 MHz.

Loading...

Loading...