InteliPro, SW version 1.4, ©ComAp –April 2014

InteliPro 1.4 Comprehensive Guide - rev. 1

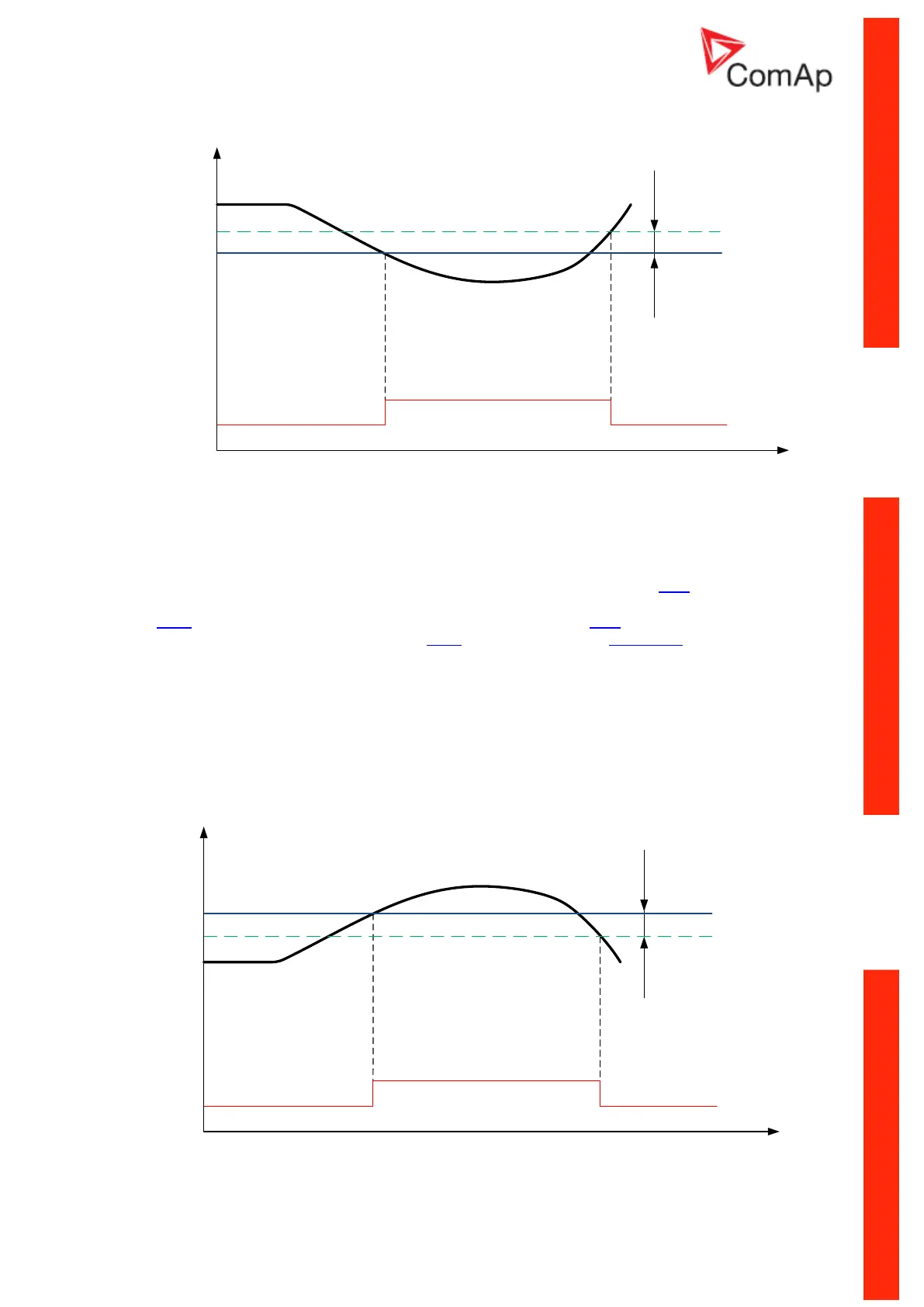

Voltage hysteresis for unervoltage

Overfrequency, Underfrequency (ANSI 81 H, L)

The frequency value measured on phase L1 is compared with the preset limit of overfrequency or

underfrequency. When any of the preset limits is over/underreached, the output f Sig moves to fault-

indicating position immediately. If the frequency keeps out of limits for the delay of the appropriate

stage, TRIP is issued. As the frequency returns back within limits, the f Sig output stops to signal the

fault state immediately, regardless of whether TRIP was issued or not or Fault reset was performed or

not.

Both overfrequency and underfrequency protective stages provide possibility of setting 2 levels with

independent delay assigned to each level.

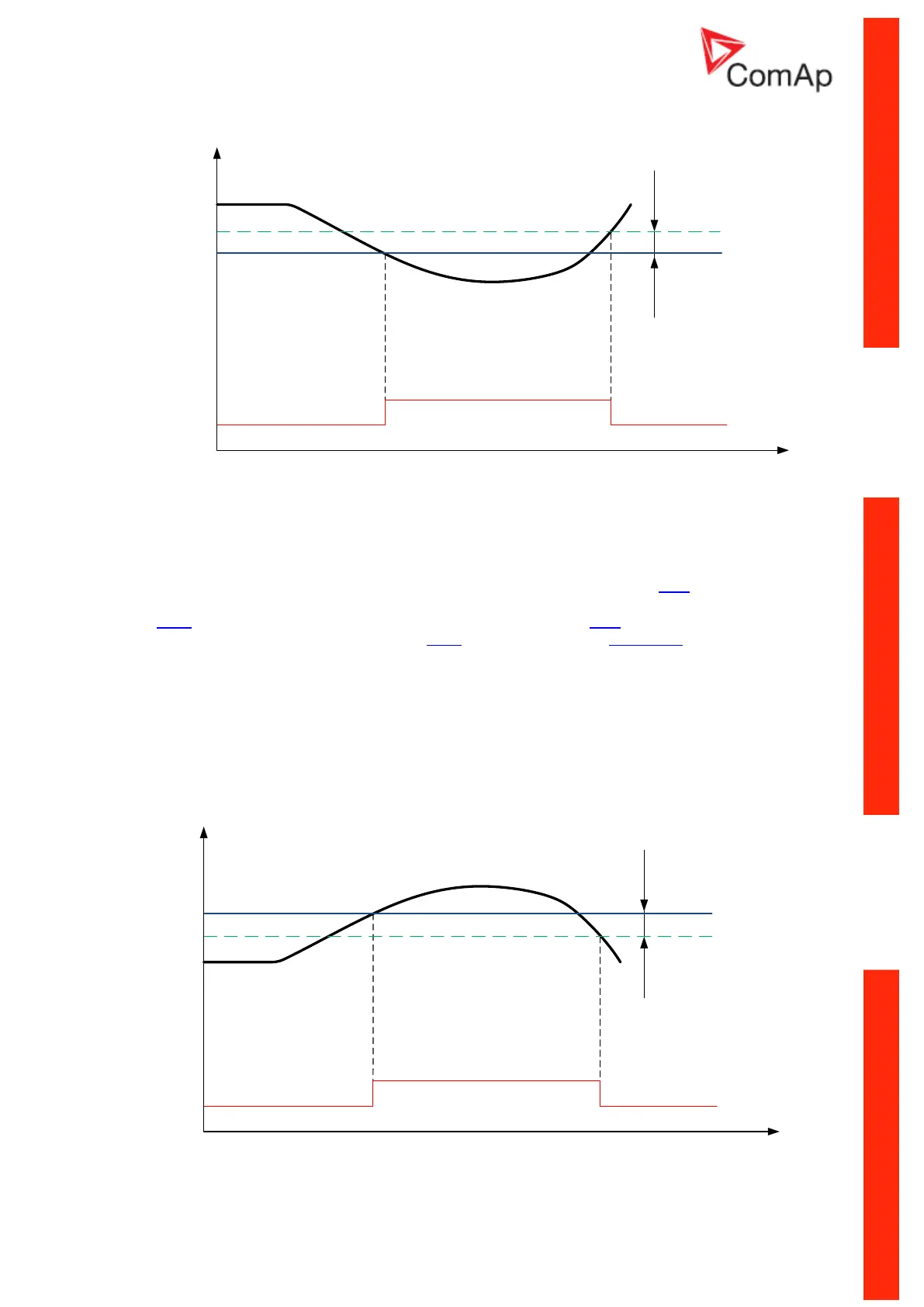

In order to prevent from unwanted frequency oscillation around the overfrequency, respective

underfrequency limits, there is a possibility to set up frequency hysteresis. The principle is shown in

the pictures below. After overfrequency situation, frequency must decrease under the hysteresis limit

to clear the fault. After underfrequency situation, frequency must exceed the hysteresis limit to clear

the fault.

Loading...

Loading...