48

INOVANCE TECHNOLGY EUROPE GmbH

SV660N Startup Procedure_EN_v1.4_20220826.docx

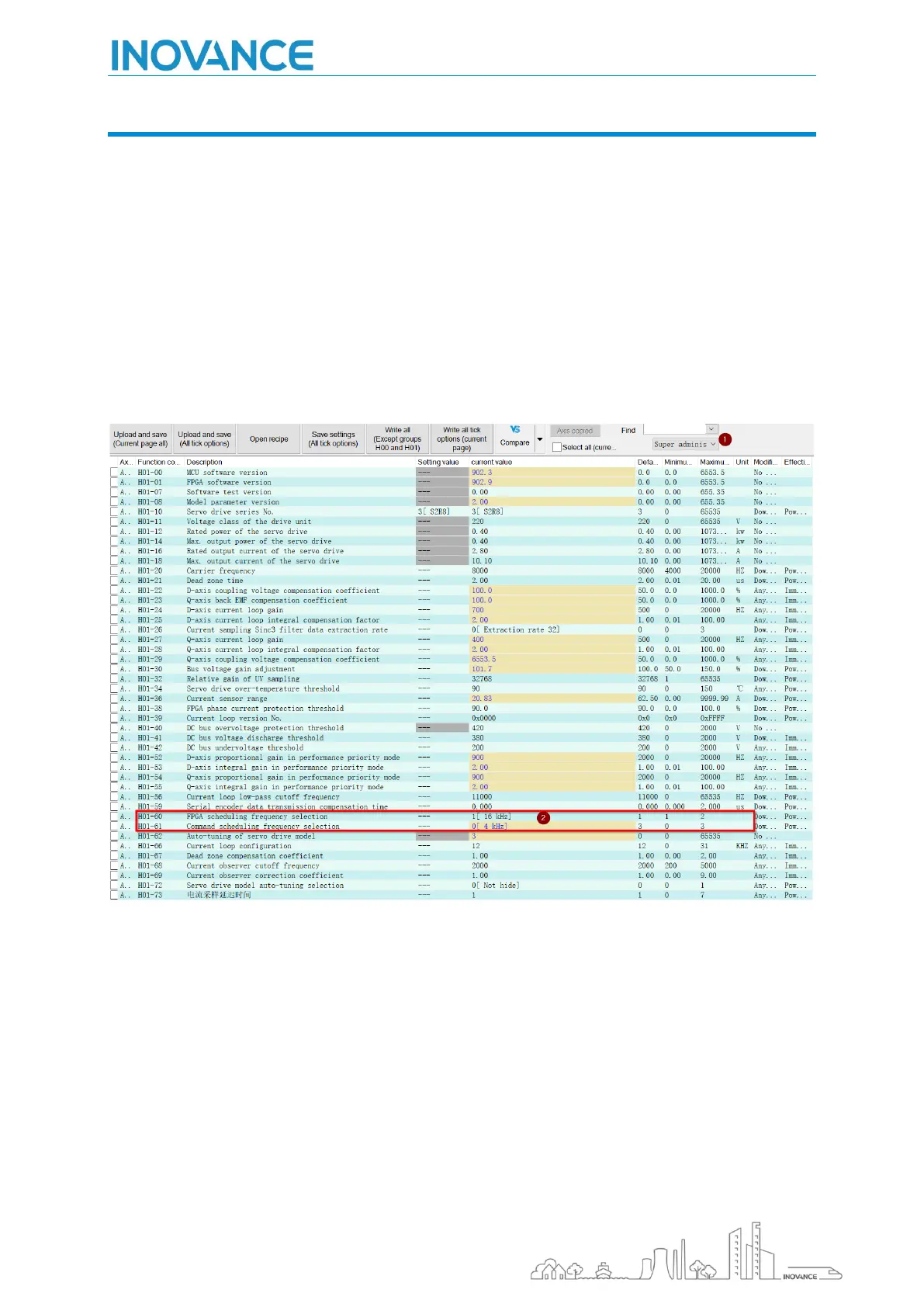

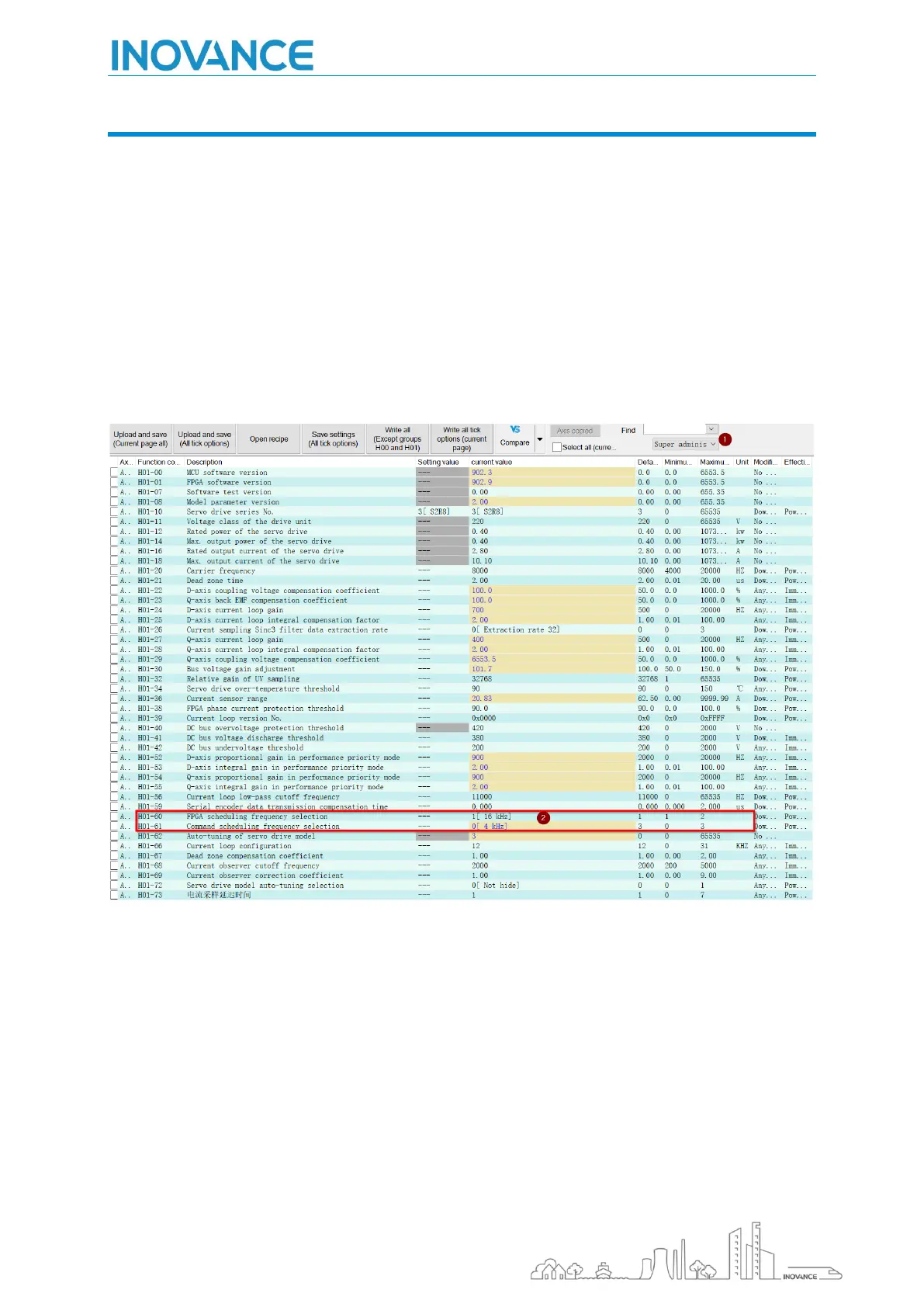

9.2 DRIVE LOOPS CYCLE TIME

By default the drive loops cycles are:

• Position command: refresh frequency of position command, related to the par H01-61 command

scheduling frequency, 1 kHz/2 kHz /4 kHz /8 kHz, sample cycle up to 125µs, default 4 kHz, 250 µs.

• Position loop cycle: related to the par H01-60 FPGA scheduling frequency, 8KHz/16Khz, sample cycle

up to 62.5µs, default 16 kHz, 62.5 µs.

• Velocity loop cycle: related to the par H01-60 FPGA scheduling frequency, 8 kHz /16 kHz, sample cycle

up to 62.5µs, default 16 kHz, 62.5 µs.

• Current loop cycle: 1.6 µs, 625 kHz, cannot be modified.

To change the cycle of the position or speed loop, it is necessary to activate the super user mode with the

password: “SuperAdmin” or H02-41 = 1430 (factory password)

Loading...

Loading...