365

NDIS, NDISP, NUNI, NUNIP

1

2

3

4

4

6

7

8

7.5 Data processing instructions

7.5.8 NDIS, NDISP, NUNI, NUNIP

: Head number of the devices where data to be dissociated/linked is stored (BIN 16 bits)

: Head number of the devices where the dissociated/linked data will be stored (BIN 16 bits)

: Head number of the devices where the units of dissociation/linking will be stored (BIN 16 bits)

Function

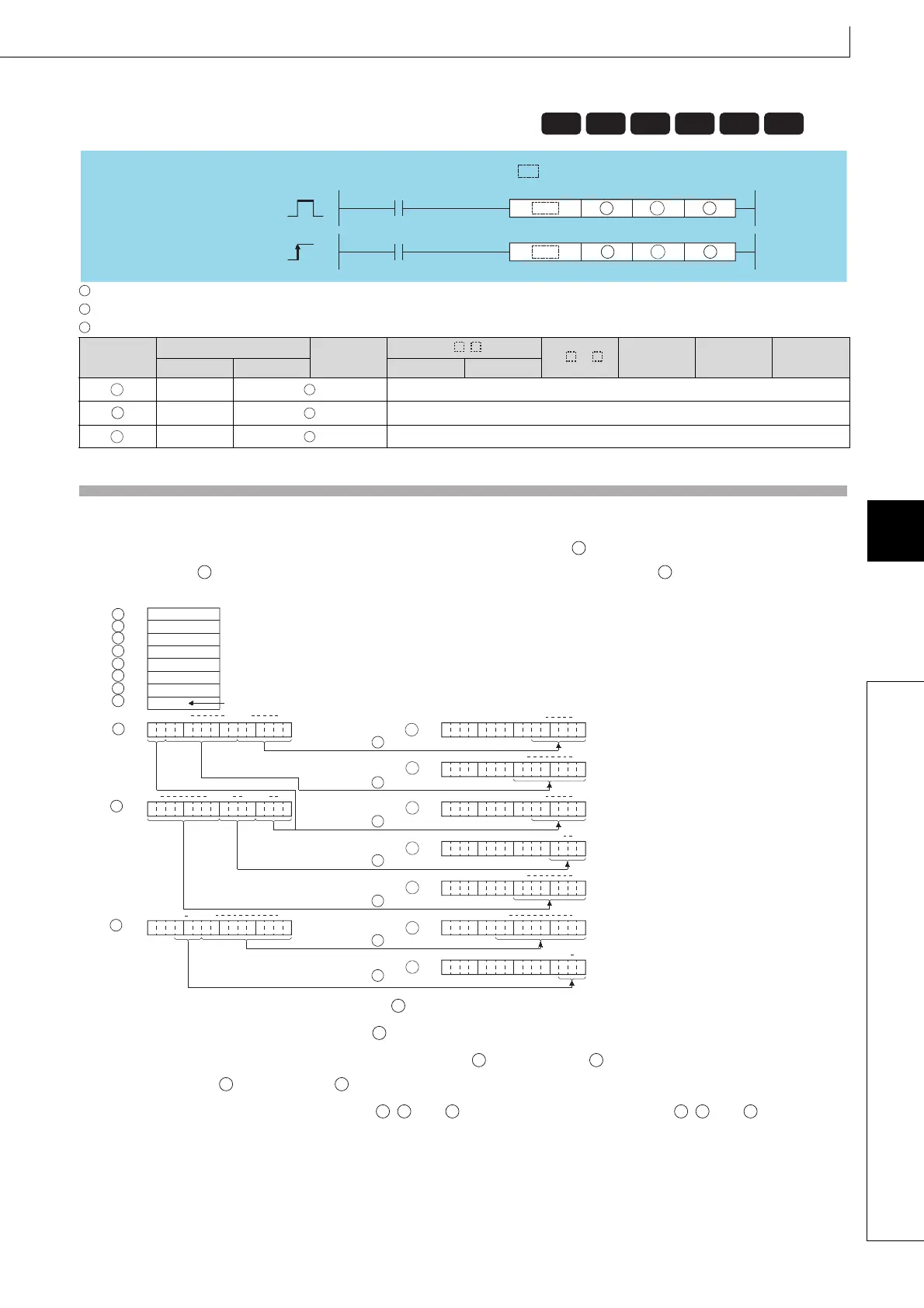

NDIS

(1) Dissociates data stored in device numbers starting from that designated at into the number of individual bits

designated at , and stores this data in device numbers starting from that designated at .

(2) The number of dissociated bits designated at can be designated within a range of 1 to 16 bits.

(3) Bits from the device number designated at to the device number where "0" is stored are processed as dissociated bits.

(4) Do not overlap the device range for data to be dissociated ( to end range of ) with the device range which stores the

dissociated data ( to end range of ). If overlapped, the correct operation result may not be obtained.

(5) Do not specify the same device number for , , and . If the same device is specified for , , and , the operation

does not work correctly.

7.5.8 NDIS, NDISP Di ssociation of ra ndom data

NUNI, NUNIP L inking of random data

7.5.8

NDIS, NDISP, NUNI, NUNIP

Setting

Data

Internal Devices

R, ZR

J\

U\G

Zn Constants Other

Bit Word Bit Word

–– ––

–– ––

–– ––

Basic

Process

High

performance

Redundant

Universal

LCPU

Command

Command

P

NDIS, NUNI

NDISP, NUNIP

S1

S2

S1

D

S2

D

indicates an instruction symbol of NDIS/NUNI.

S1

D

S2

S1

D

S2

S1

S2

D

Number of bits

designated at

6

4

8

3

0

Designation of the end of setting

Designation of the number of dissociated bits

b0

b5

b0

b7

b0

b5

b0

b3

b0

b7

b0

b9

b0

b2

b0

b5b6b15

b14

b13

b8

b15 b3 b0b4

b7

b12 b10 b0b9

8

6

10

S1

S2

D

S2

S2

S2

S2

S2

S2

S2

S1

S

1

S2

D

D

D

D

D

D

+1

+1

+2

+3

+4

+5

+6

+7

+1

+2

+6

+5

+4

+3

Number of bits

designated at +1

S2

Number of bits

designated at +2

S2

Number of bits

designated at +3

S2

Number of bits

designated at +4

S2

Number of bits

designated at +5

S2

Number of bits

designated at +6

S2

S2

S2

S1 S1

D D

S1

S2

D

S1

S2

D

Loading...

Loading...