3-36 Theory of Operation: Controller

3.2.4.7 Double Data Rate (DDR) Memory (U6301)

The 32MB DDR Synchronous DRAM IC is interfaced to the OMAP using 13 address bits and a 16bit

data bus. The DDR IC is driven by a complementary clock signal originating from the OMAP IC. The

DDR clock is initialized to 96 MHz by the OMAP boot code. Additional control signals are also

dedicated for the DRAM interface

.

3.2.4.8 Peripheral Devices

The OMAP processor is equipped with multiple buses and interfaces that are configured for

peripheral interconnection.

3.2.4.8.1 Receive and Transmit SSI

These two interfaces are dedicated for communicating with the RF deck digital interface, carrying

receive and transmit base band signals. The OMAP processor generates the clock and FSYNC

signals for the receive SSI interface. The RF deck generates these signals for the transmit SSI

interface.

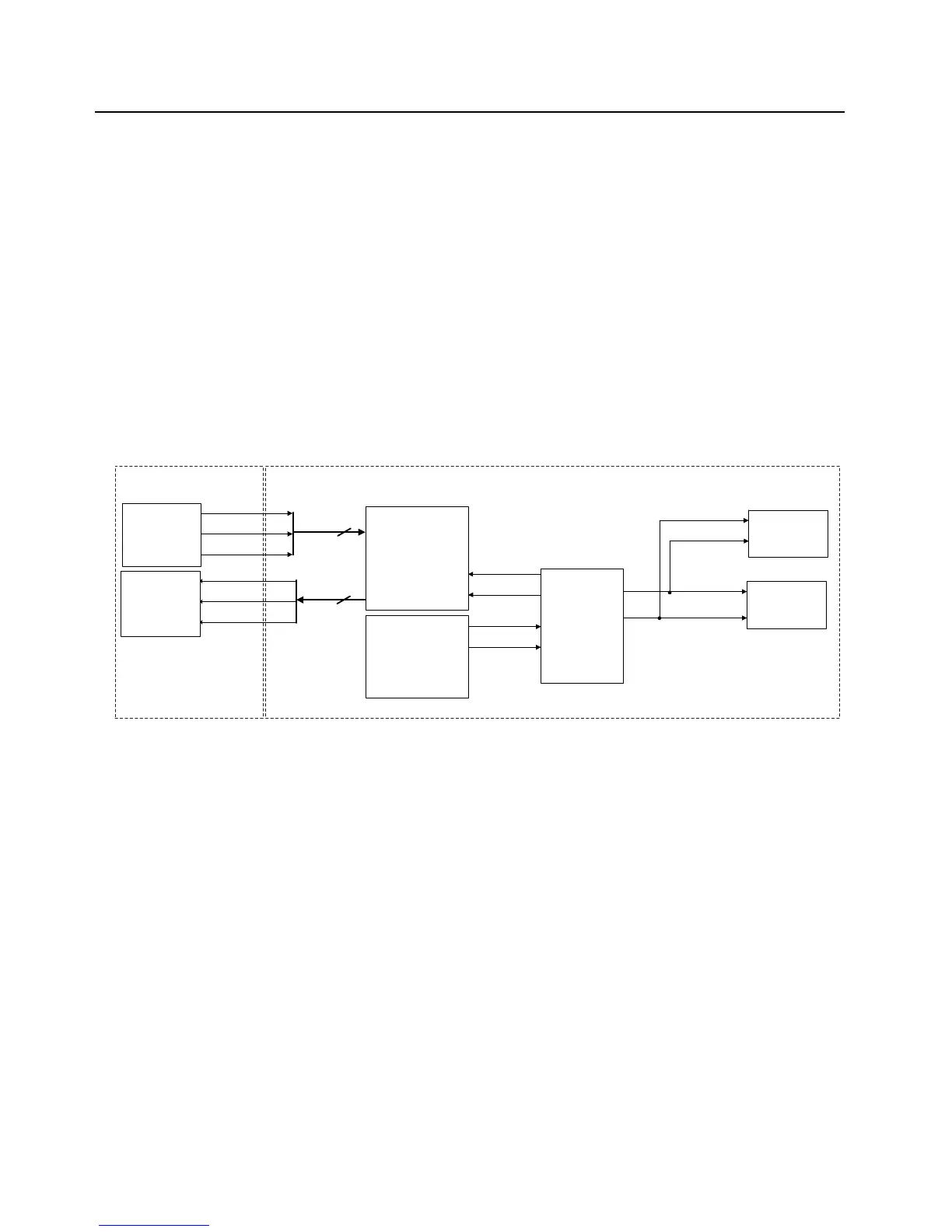

Figure 3-26. RX/ TX SSI Configuration

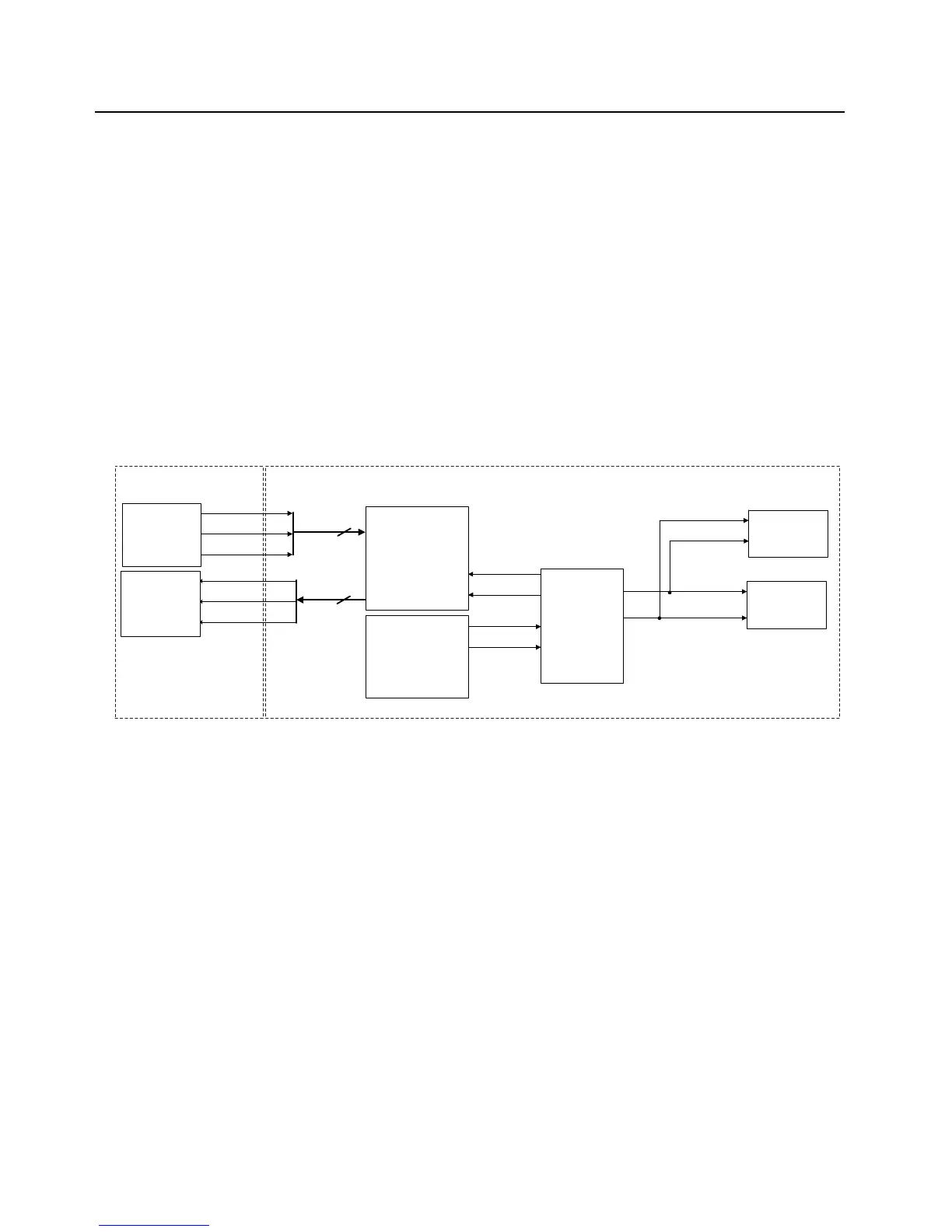

3.2.4.8.2 Audio SSI

OMAP's McBSP1 interface is configured as a SSI interface dedicated to carry transmit and receive

audio data to peripheral devices. The peripherals connected to this bus include MAKO, Audio

CODEC, MACE and CPLD. The bus also connects to the keypad board. MAKO generates the clock

and frame sync signals for this bus.

RF SECTION

TRIDENT

ABACUS

RX_FSYNC

RX_CLK

RX_DA

TX_FSYNC

TX_CLK

TX_DA

CONTROLLER SECTION

OMAP 1710

MAKO

TI

CODEC

MACE

McBSP 2

McBSP 1

RX SSI

TX SSI

3

3

VC_FSYNC

VC_DCLK

SYNC

BCLK

MACE/CODEC

FSYNC

MACE/

CODEC_CLK

McBSP 2

CPLD

MCLK

WCLK

Loading...

Loading...