8

8-27

INPUT/OUTPUT PORTS AND PIN FUNCTIONS

32180 Group User’s Manual (Rev.1.0)

8.5 Port Peripheral Circuits

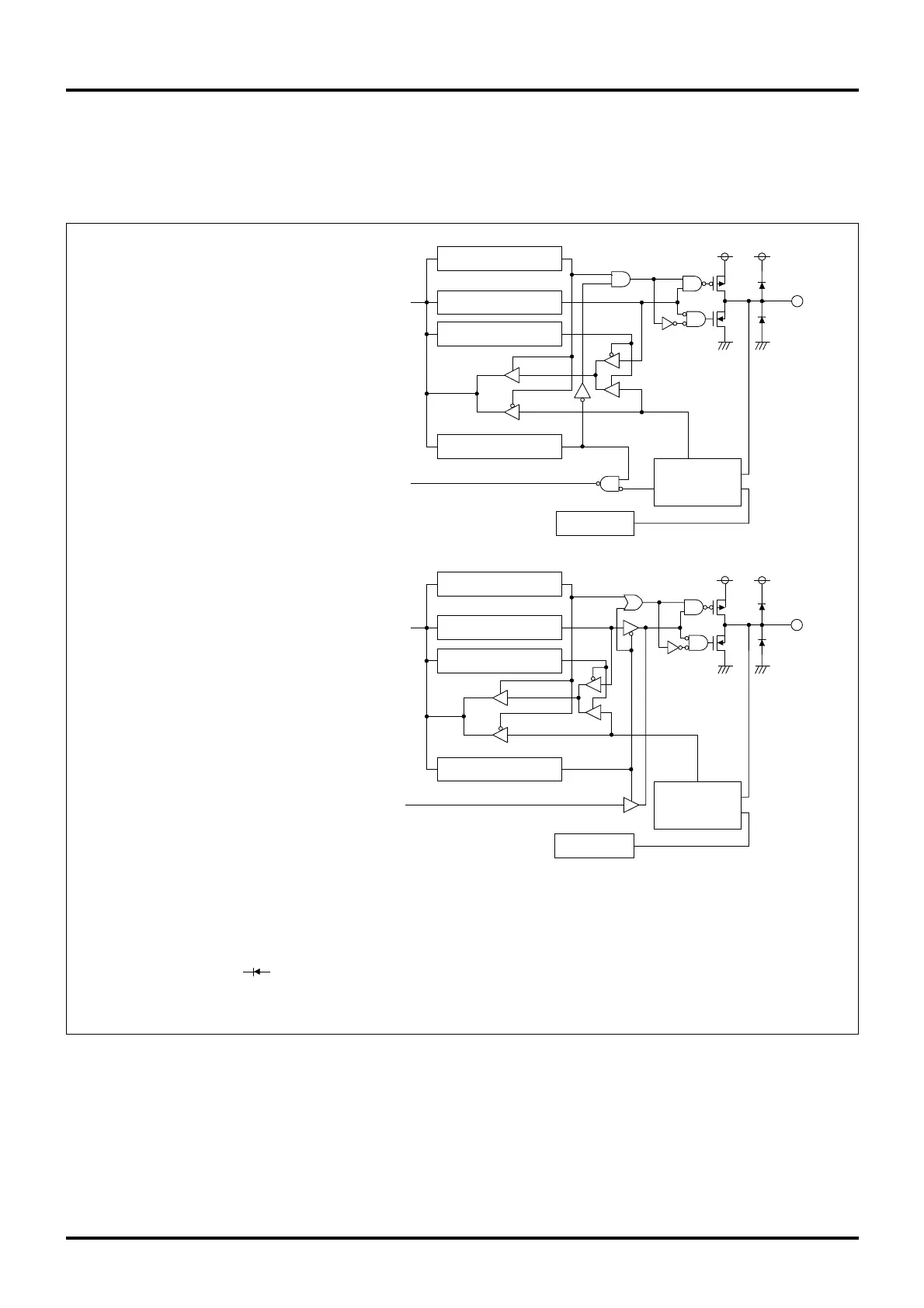

Figures 8.5.1 through 8.5.4 show the peripheral circuit diagrams of the input/output ports described in the preced-

ing pages.

Figure 8.5.1 Port Peripheral Circuit Diagram (1)

Data bus

Operation mode register

Input function

enable

Peripheral function input

Port output latch

Direction register

Input data select bit

Port level

switching function

(Standard:

peripheral TTL)

P44(CS0#)

P45(CS1#)

P70(BCLK/WR#)

P82(TXD0)

P85(TXD1)

P93–P97(TO16–TO20)

P100(TO8)

P103–P107(TO11–TO15)

P110–P117(TO0–TO7)

P166, P167(TO27, TO28)

P174(TXD2)

P176(TXD3)

P186, P187(TO35, TO36)

P200(TXD4)

P202(TXD5)

P216, P217(TO43, TO44)

P220(CTX0)

P222(CTX1)

P226(CS2#)

P227(CS3#)

P00–P07(DB0–DB7)

P10–P17(DB8–DB15)

P20–P27(A23–A30)

P30–P37(A15–A22)

P46, P47(A13, A14)

P71(WAIT#)

P73(HACK#)

P74(RTDTXD)

P76(RTDACK)

P224(A11/CS2#)

P225(A12/CS3#)

(Note 1)

Data bus

Operation mode register

Input function

enable

Peripheral function input

Port output latch

Direction register

Input data select bit

Port level switching

function (No

peripheral input)

(Note 1)

Note 1: For details about the port level switching function, see Section 8.4, "Port Input Level Switching Function."

Notes: • During processor mode, P00-P07, P10-P17, P20-P27, P30-P37, P45-P47, P224, and P225 are external bus

interface control signal pins, but their functional description in this block diagram is omitted.

• Although P224 and P225 serve triple functions, their functional description in this block diagram is omitted.

• The circle denotes a pin.

• The symbol denotes a parasitic diode. Make sure the voltage applied to each pin does not exceed the

VCCE voltage.

• The input capacitance of each pin is approximately 10 pF.

8.5 Port Peripheral Circuits