4

4-8

EIT

32180 Group User’s Manual (Rev.1.0)

4.5 Acceptance of EIT Events

When an EIT event occurs, the CPU suspends the program it has hitherto been executing and branches to EIT

processing by the relevant handler. Conditions under which each EIT event occurs and the timing at which they are

accepted are shown below.

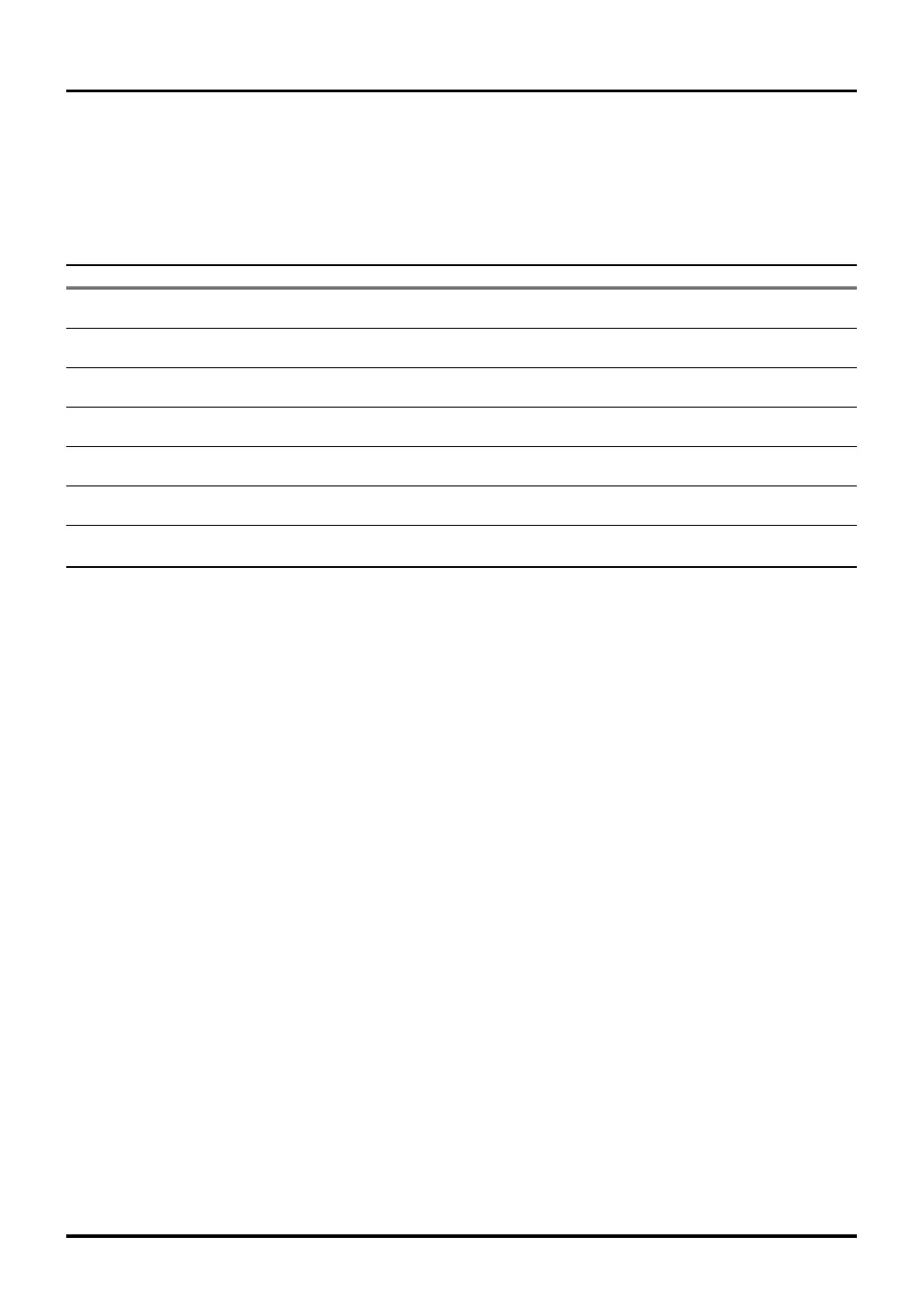

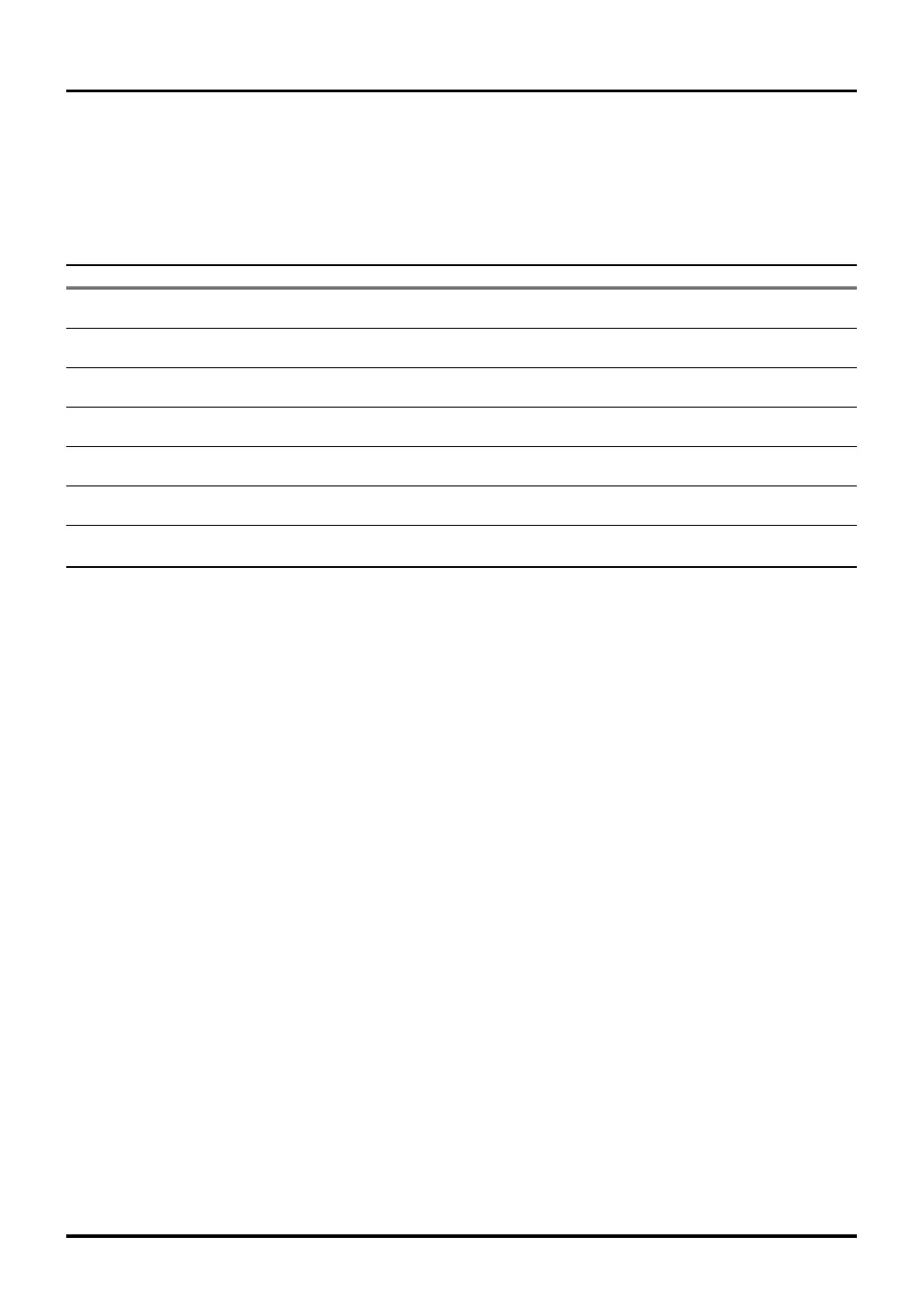

Table 4.5.1 Acceptance of EIT Events

EIT Event Type of Processing Acceptance Timing Values Set in BPC Register

Reserved Instruction Instruction processing- During instruction execution PC value of the instruction that

Exception (RIE) canceled type generated RIE

Address Exception (AE) Instruction processing- During instruction execution PC value of the instruction that

canceled type generated AE

Floating-Point Exception Instruction processing- Break in instructions PC value of the instruction that

(FPE) completed type generated FPE + 4

Reset Interrupt (RI) Instruction processing- Each machine cycle Undefined value

aborted type

System Break Interrupt Instruction processing- Break in instructions PC value of the next instruction

(SBI) completed type (word boundary only)

External Interrupt (EI) Instruction processing- Break in instructions PC value of the next instruction

completed type (word boundary only)

Trap (TRAP) Instruction processing- Break in instructions PC value of TRAP instruction + 4

completed type

4.6 Saving and Restoring the PC and PSW

The following describes operation of the microcomputer at the time when it accepts an EIT and when it executes the

RTE instruction.

(1) Hardware preprocessing when an EIT is accepted

[1] Save the PSW register’s SM, IE and C bits in its backup field.

BSM ← SM

BIE ← IE

BC ← C

[2] Update the PSW register’s SM, IE and C bits

SM ← Remains unchanged (RIE, AE, FPE, TRAP) or cleared to "0" (SBI, EI, RI)

IE ← Cleared to "0"

C ← Cleared to "0"

[3] Save the PC register

BPC ← PC

[4] Set the vector address in the PC register

Branches to the EIT vector and executes the branch (BRA) instruction written in it, thereby transferring

control to the user-created EIT handler.

(2) Hardware postprocessing when the RTE instruction is executed

[A] Restore the PSW register’s SM, IE and C bits from its backup field.

SM ← BSM

IE ← BIE

C ← BC

[B] Restore the PC register from the BPC register.

PC ← BPC

Note: • The values stored in the BPC and the PSW register’s BSM, BIE and BC bits after executing the RTE

instruction are undefined.

4.5 Acceptance of EIT Events

Loading...

Loading...