15

15-10

EXTERNAL BUS INTERFACE

32180 Group User’s Manual (Rev.1.0)

15.3 Read/Write Operations

(1) When the Bus Mode Control Register = "0"

External read/write operations are performed using the address bus, data bus and the signals CS0#–CS3#,

RD#, BHW#, BLW#, WAIT# and BCLK. In the external read cycle, the RD# signal is low while BHW# and

BLW# both are high, with data read in from only the necessary byte position. In the external write cycle, the

BHW# or BLW# signal output for the byte position to which to write is asserted low as data is written to the

bus.

When an external bus cycle starts, wait states are inserted as long as the WAIT# signal is low. Unless

necessary, the WAIT# signal must always be held high.

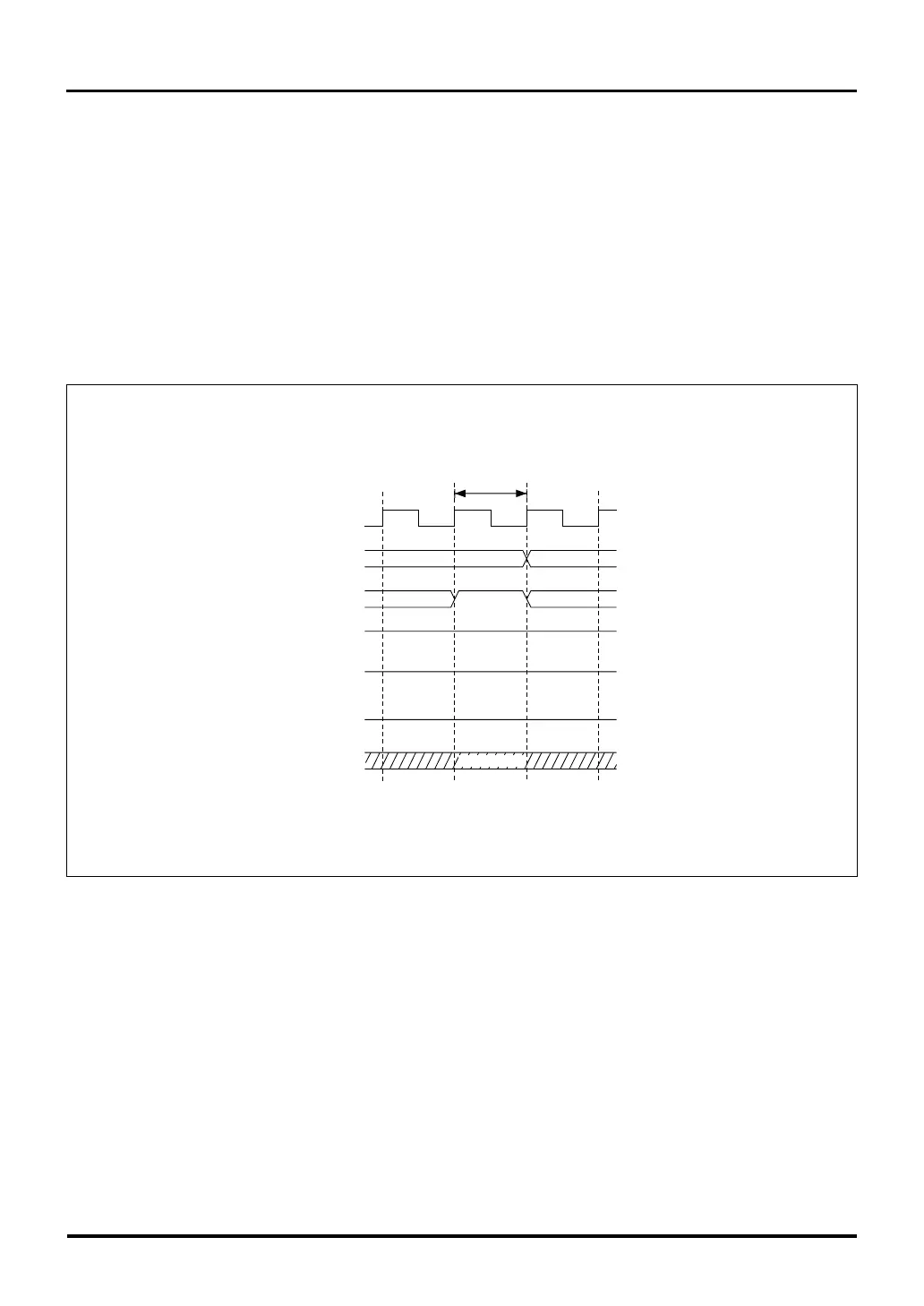

Figure 15.3.1 Internal Bus Access during Bus Free State

15.3 Read/Write Operations

Bus-free state

Internal bus access

"H"

BCLK

A11–A30

CS0#–CS3#

BHW#, BLW#

DB0–DB15

WAIT#

RD#

"H"

Hi-z

Note 1: For details about the Bus Mode Control Register, see Section 15.2.3, "Bus Mode Control Register."

Note: • Hi-Z denotes a high-impedance state.

(Don't Care)

Bus Mode Control Register (Note 1)

BUSMOD bit = 0 (WR signal separated)