TPS-1 User’s Manual: Hardware 4. Shared memory structure

R19UH0081ED0107 Rev. 1.07 page 36 of 86

Jul 30, 2018

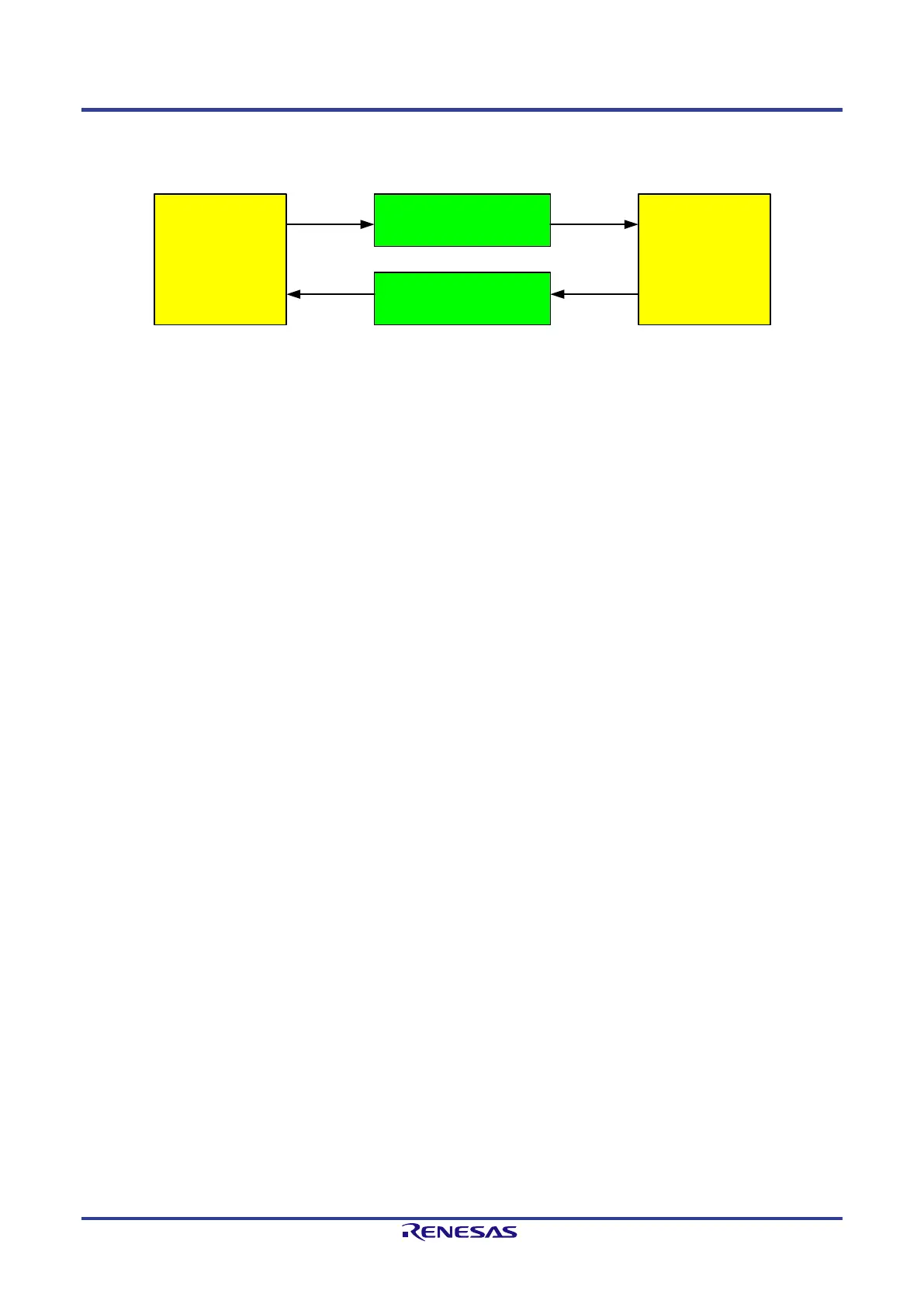

4.1. Event communication with the TPS-1 Firmware

After system start up the communication between the TPS-1 and the host CPU is processed by the event register (one register for each direction). Each

bit of the event register causes a special action.

Event Register

TPS-1

(32-Bit)

Event Register

Application CPU

(32 Bit)

Host

Application

CPU

TPS-1

PROFINET

CPU

Write

Read

Read

Write

Figure 4-3: TPS-1 Event Communication

For process changes of the event register the TPS-1 and the host CPU has to poll these registers. You can also use an interrupt control mode if the host

CPU supports this.

The event bits corresponding to the mail box access are not ambiguous. After receiving this event it is necessary to check each mail box. In the header

of the respective mail box, the READ_FLAG is set.

The following tables describe the structure of the event register for each direction.

For each possible event bit in the event register a special callback function is implemented. For example, the event

“EVENT_ONCONNECT_REQ_REC_0” (bit 13) indicates a Connect.Req for the first AR (AR0). In this case the check function will call in the

function OnConnect() and process the event.