TPS-1 User’s Manual: Hardware 10. Reset of the TPS-1

R19UH0081ED0107 Rev. 1.07 page 58 of 86

Jul 30, 2018

10. Reset of the TPS-1

An external reset is caused by a “low” level at the signal pin RESETN. This condition is held until the “low” level changes to a “high” level.

During startup of the power supply the 3.3 V voltage is controlled by the TPS-1 (internal). The 1.5 V voltage (if fed from external) and the 1.0 V

voltage must be controlled by an external circuitry.

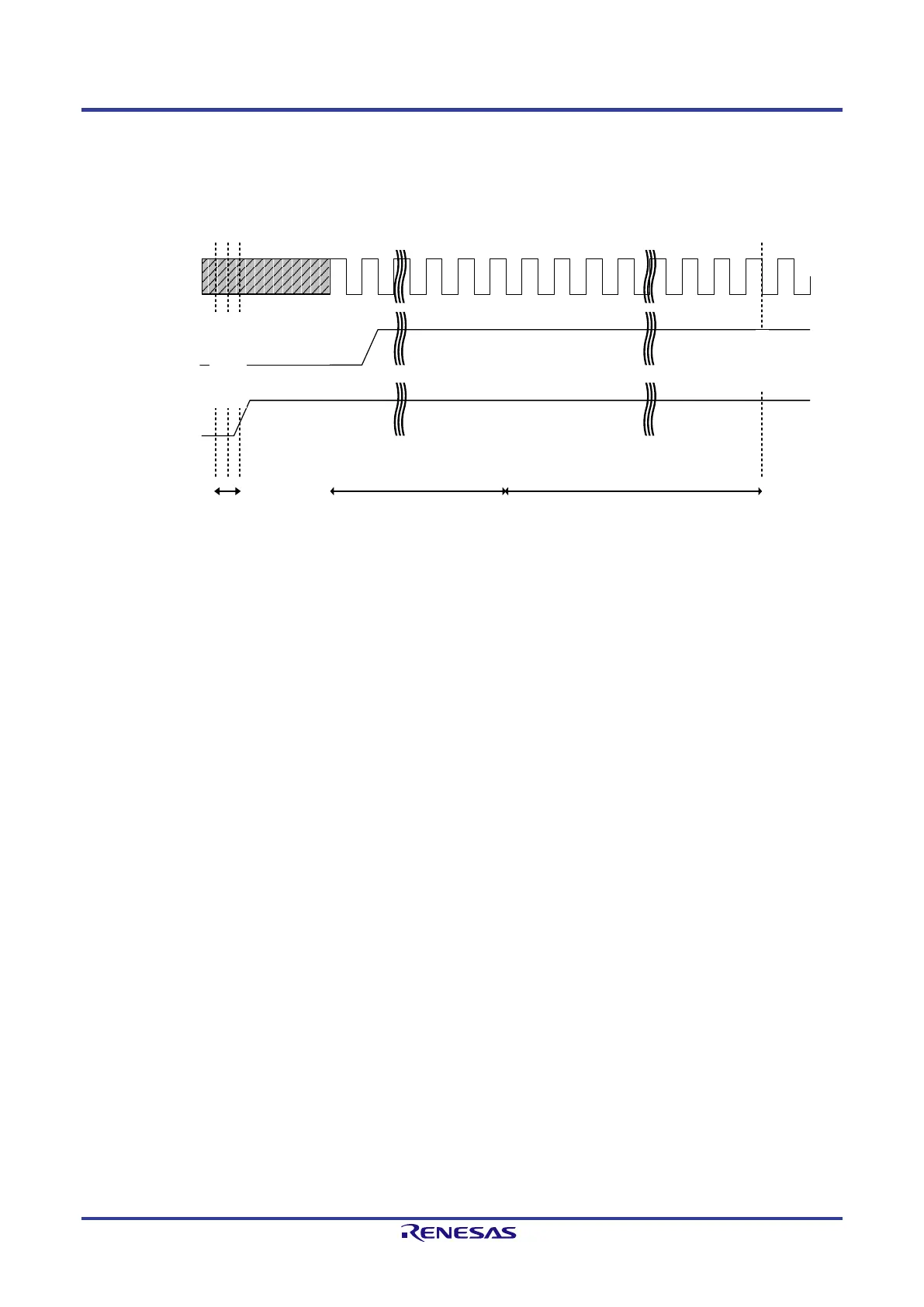

10 us 30us 500us

OSC_CLK

(25 MHz)

RESETN

(external)

POR_OUT

(internal)

3.3 V supply stable

1.5 V supply stable

PLL locked

1.0 V supply stable

Figure 10-1: Reset behavior

The start-up time of the oscillator depends on the external components (quartz, RLC). As a general rule of thumb, it is roughly in the range

of 5 to 20 ms and at higher temperatures in the range of 80 ms.

Annotation:

A hardware reset during operation does not change the configuration of GPIO pins and the pins keep their state during the reset

phase. When a signal e.g. was configured as an output, the last state is not changed and the output is driven further with the last

signal level.

Loading...

Loading...