TPS-1 User’s Manual: Hardware 11. Boundary Scan Interface (JTAG)

R19UH0081ED0107 Rev. 1.07 page 59 of 86

Jul 30, 2018

11. Boundary Scan Interface (JTAG)

The JTAG interface is used for the Boundary Scan test.

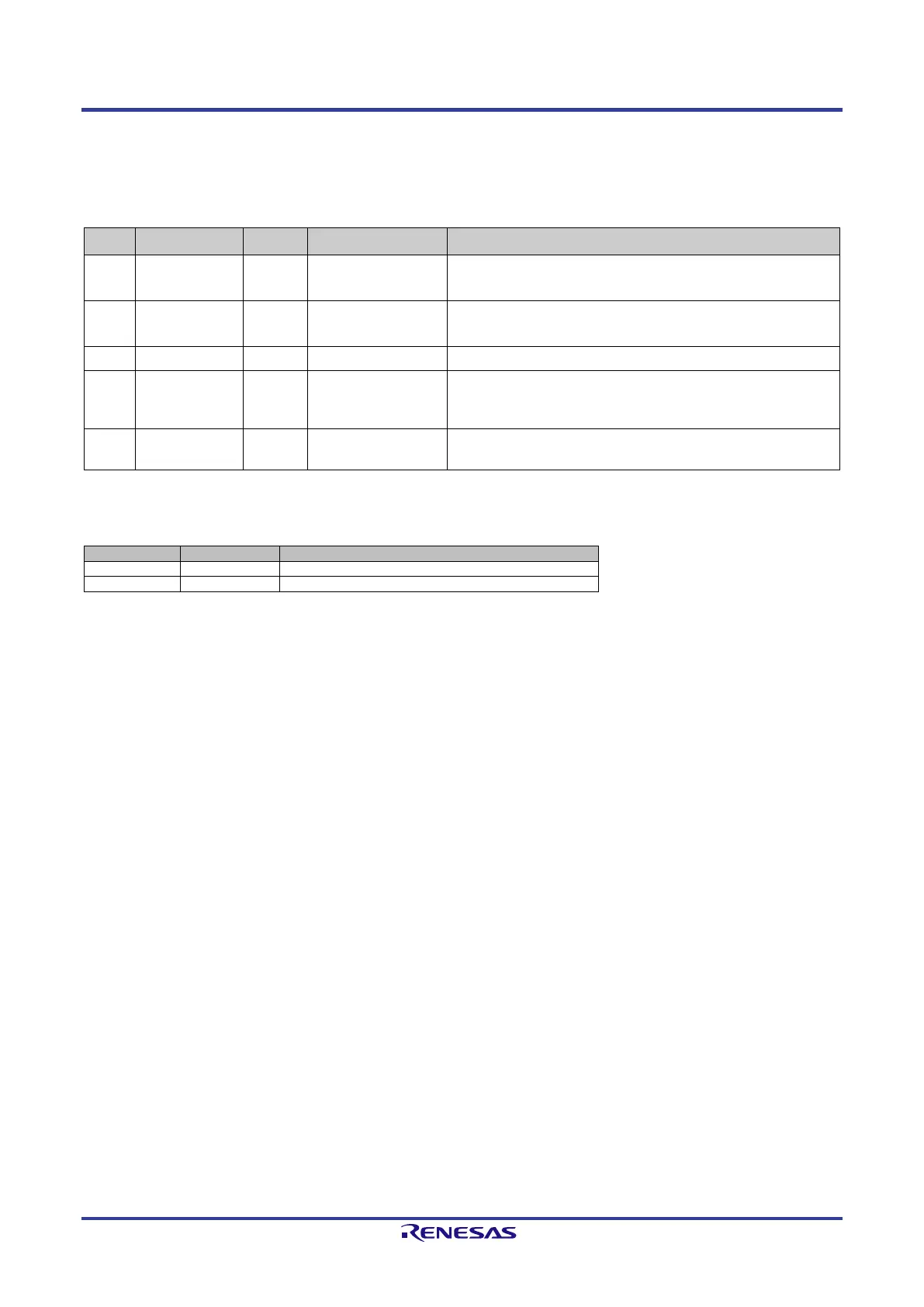

Table 11-1: JTAG interface pin definition

Pin Designation Type Description Remark

K5 TRSTN I Test Reset JTAG Reset. Input: Reset signal of the target port.

External pull-down (4K7 Ω to GND)

JTAG interface is activated from the debug unit.

pull-up (4K7 Ω to V

DD

)

L7 TDO O Test Data Output

JTAG clock signal to the TPS-1. It is recommended that

this pin be set to a defined state on the target board.

External pull-up (4K7 Ω to V

DD

)

L5 TDI I Test Data Input External pull-up

(4K7 Ω to V

DD

)

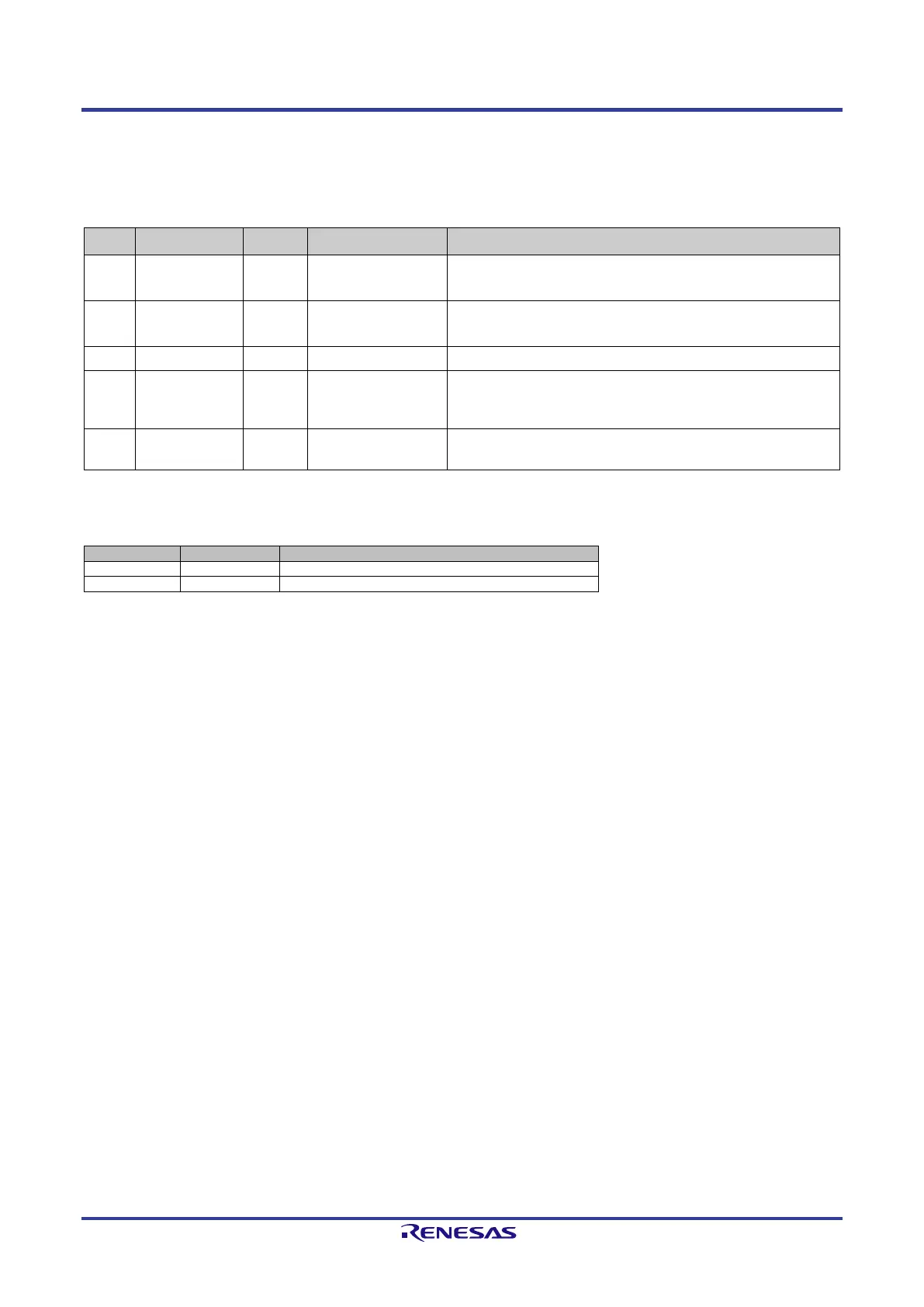

Table 11-2: JTAG interface pin definition

Boundary scan mode (see BSDL file)

Loading...

Loading...