36 www.xilinx.com VC707 Evaluation Board

UG885 (v1.4) May 12, 2014

Chapter 1: VC707 Evaluation Board Features

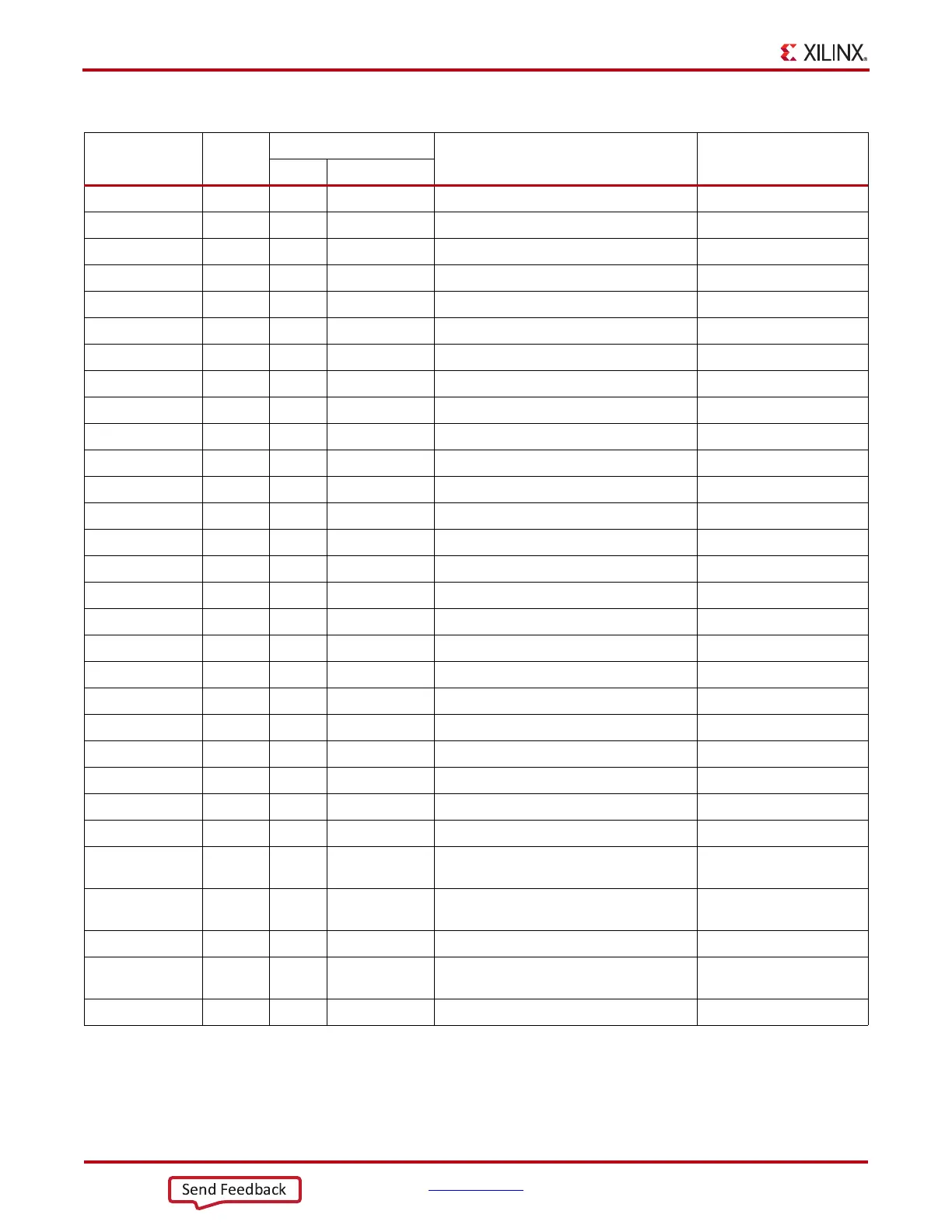

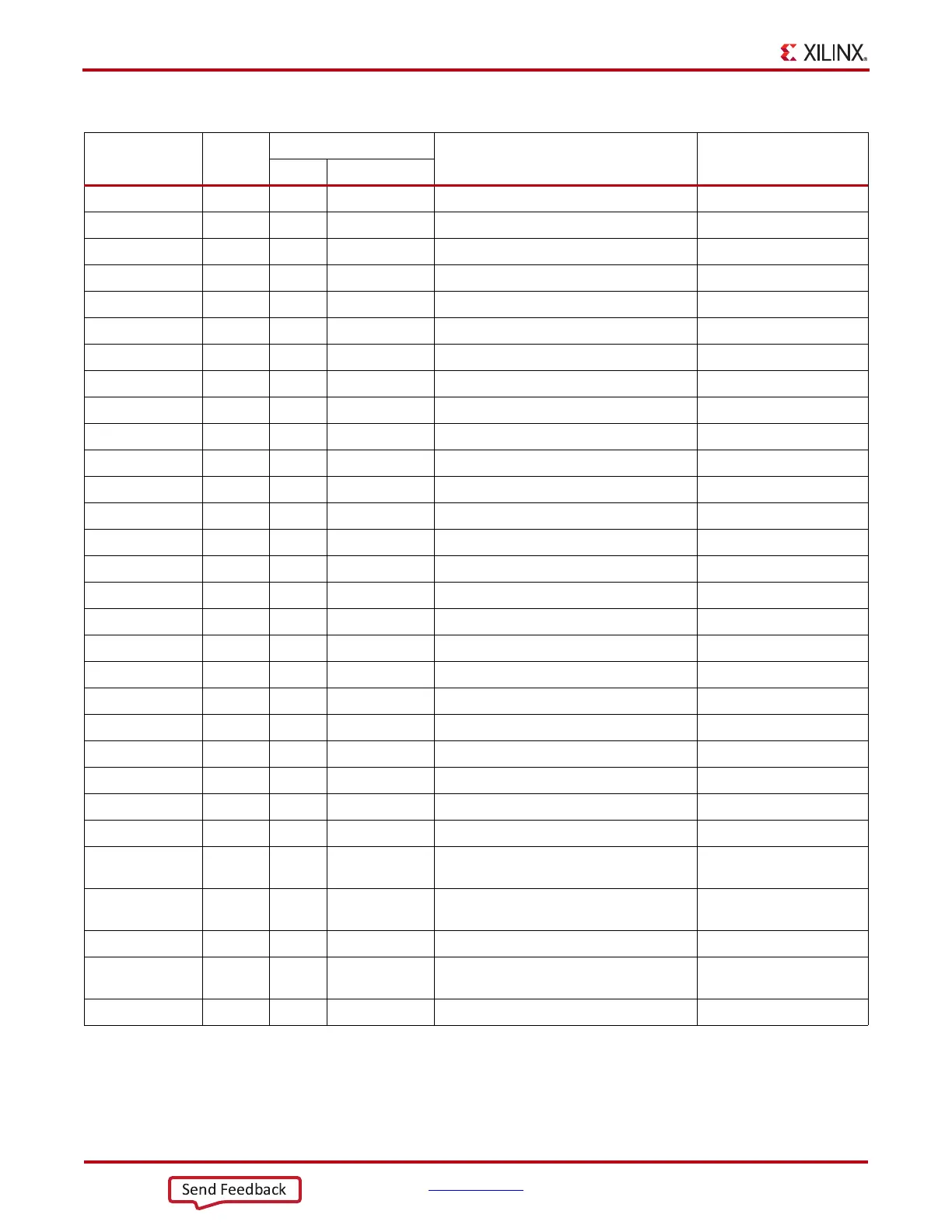

PCIE_RX3_N AC5 B28 PETn3 Integrated Endpoint block receive pair GTXE2_CHANNEL_X1Y8

PCIE_RX4_P AD4 B33 PETp4 Integrated Endpoint block receive pair GTXE2_CHANNEL_X1Y7

PCIE_RX4_N AD3 B34 PETn4 Integrated Endpoint block receive pair GTXE2_CHANNEL_X1Y7

PCIE_RX5_P AE6 B37 PETp5 Integrated Endpoint block receive pair GTXE2_CHANNEL_X1Y6

PCIE_RX5_N AE5 B38 PETn5 Integrated Endpoint block receive pair GTXE2_CHANNEL_X1Y6

PCIE_RX6_P AF4 B41 PETp6 Integrated Endpoint block receive pair GTXE2_CHANNEL_X1Y5

PCIE_RX6_N AF3 B42 PETn6 Integrated Endpoint block receive pair GTXE2_CHANNEL_X1Y5

PCIE_RX7_P AG6 B45 PETp7 Integrated Endpoint block receive pair GTXE2_CHANNEL_X1Y4

PCIE_RX7_N AG5 B46 PETn7 Integrated Endpoint block receive pair GTXE2_CHANNEL_X1Y4

PCIE_TX0_P W2 A16 PERp0 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y11

PCIE_TX0_N W1 A17 PERn0 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y11

PCIE_TX1_P AA2 A21 PERp1 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y10

PCIE_TX1_N AA1 A22 PERn1 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y10

PCIE_TX2_P AC2 A25 PERp2 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y9

PCIE_TX2_N AC1 A26 PERn2 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y9

PCIE_TX3_P AE2 A29 PERp3 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y8

PCIE_TX3_N AE1 A30 PERn3 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y8

PCIE_TX4_P AG2 A35 PERp4 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y7

PCIE_TX4_N AG1 A36 PERn4 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y7

PCIE_TX5_P AH4 A39 PERp5 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y6

PCIE_TX5_N AH3 A40 PERn5 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y6

PCIE_TX6_P AJ2 A43 PERp6 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y5

PCIE_TX6_N AJ1 A44 PERn6 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y5

PCIE_TX7_P AK4 A47 PERp7 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y4

PCIE_TX7_N AK3 A48 PERn7 Integrated Endpoint block transmit pair GTXE2_CHANNEL_X1Y4

Si5324_OUT_C_P AD8 A13 REFCLK+ Integrated Endpoint block differential clock

pair from PCIe

MGT_BANK_114

(not Quad 115)

Si5324_OUT_C_N AD7 A14 REFCLK- Integrated Endpoint block differential clock

pair from PCIe

MGT_BANK_114

(not Quad 115)

PCIE_PRSNT_B J49 2, 4, 6 A1 PRSNT#1 J49 Lane Size Select jumper NA

PCIE_WAKE_B AV33 B11 WAKE# Integrated Endpoint block wake signal, not

connected on KC705 Board

NA

PCIE_PERST_B AV35 A11 PERST Integrated Endpoint block reset signal NA

Table 1-12: PCIe Edge Connector Connections GTX Quad 115 (Cont’d)

Net Name

FPGA (U1)

Pin

PCIe Edge Connector (P1)

Function

FHG1761

Placement

Pin Name

Loading...

Loading...