Do you have a question about the Xilinx VC707 and is the answer not in the manual?

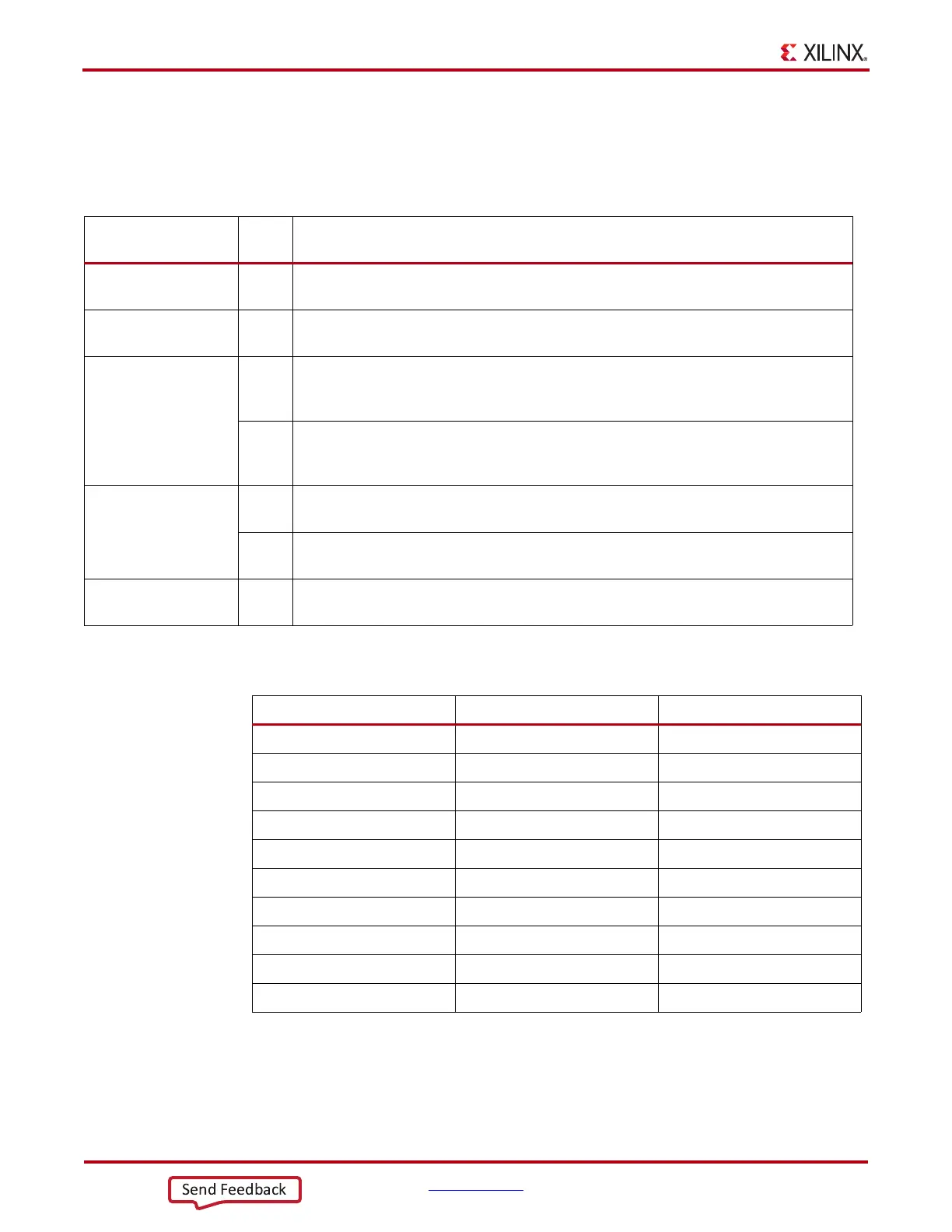

| Form Factor | ATX |

|---|---|

| FPGA Device | XC7VX485T |

| FPGA Family | Virtex-7 |

| Logic Cells | 485, 760 |

| DSP Slices | 2, 800 |

| Operating Temperature | 0°C to +85°C |

| Flash Memory | 128 Mb (for configuration) |

| Configuration | JTAG, SPI Flash |

| Connectivity | USB |

| Expansion Connectors | FMC |

| USB | USB 2.0 |

| PCIe Gen2/Gen3 Support | Yes |

| Ethernet | 1 Gbps |

| Power Supply | ATX |

General introduction to the VC707 board and its features.

Refers to external resources for additional information about the board.

Detailed descriptions of the VC707 board's hardware components and interfaces.

Details about the main FPGA chip on the VC707 board.

Information about the 1 GB DDR3 SODIMM memory module.

Details on the 128 MB nonvolatile flash memory for configuration or storage.

Information on the USB 2.0 PHY for host computer connectivity.

Description of the SDIO interface for user-logic access to memory cards.

Details about the onboard USB-to-JTAG configuration logic module.

Information on the five clock sources provided for the FPGA.

Details on the 27 GTX transceivers and their connectivity.

Information on the 8-lane PCI Express edge connector and data transfer rates.

Information on the Marvell Alaska PHY device for Ethernet communications.

Information on the HDMI video output using the Analog Devices ADV7511.

Description of the I2C port and bus switch on the board.

Definition and description of the status LEDs on the board.

Details on user LEDs, pushbuttons, DIP switches, rotary switches, and SMA connectors.

Details about the power on/off slide switch.

Information about the FPGA programming pushbutton.

Details on DIP switch SW11 for configuration mode and flash address.

Details on the VITA 57.1 FMC1 and FMC2 HPC connectors.

Overview of the board's power distribution system.

Details about the XADC block and its capabilities.

Default settings for the 8-position GPIO DIP switch SW2.

Default settings for SW11, controlling configuration mode and flash address.

List of default jumper positions for various board connectors.

Pinout diagram for the FMC1 HPC connector (J35).

Pinout diagram for the FMC2 HPC connector (J37).

Master Xilinx design constraints (XDC) file template for VC707 board designs.

Step-by-step guide for installing the board into a PC chassis.

Physical dimensions of the VC707 evaluation board.

Operating temperature, storage, and humidity specifications.

List of websites and documents for up-to-date information and supplemental material.

Details on the product's conformity to EU directives and standards.

Information on radio disturbance and immunity characteristics.

Safety requirements for information technology equipment.