76 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 5: Tile Features

R

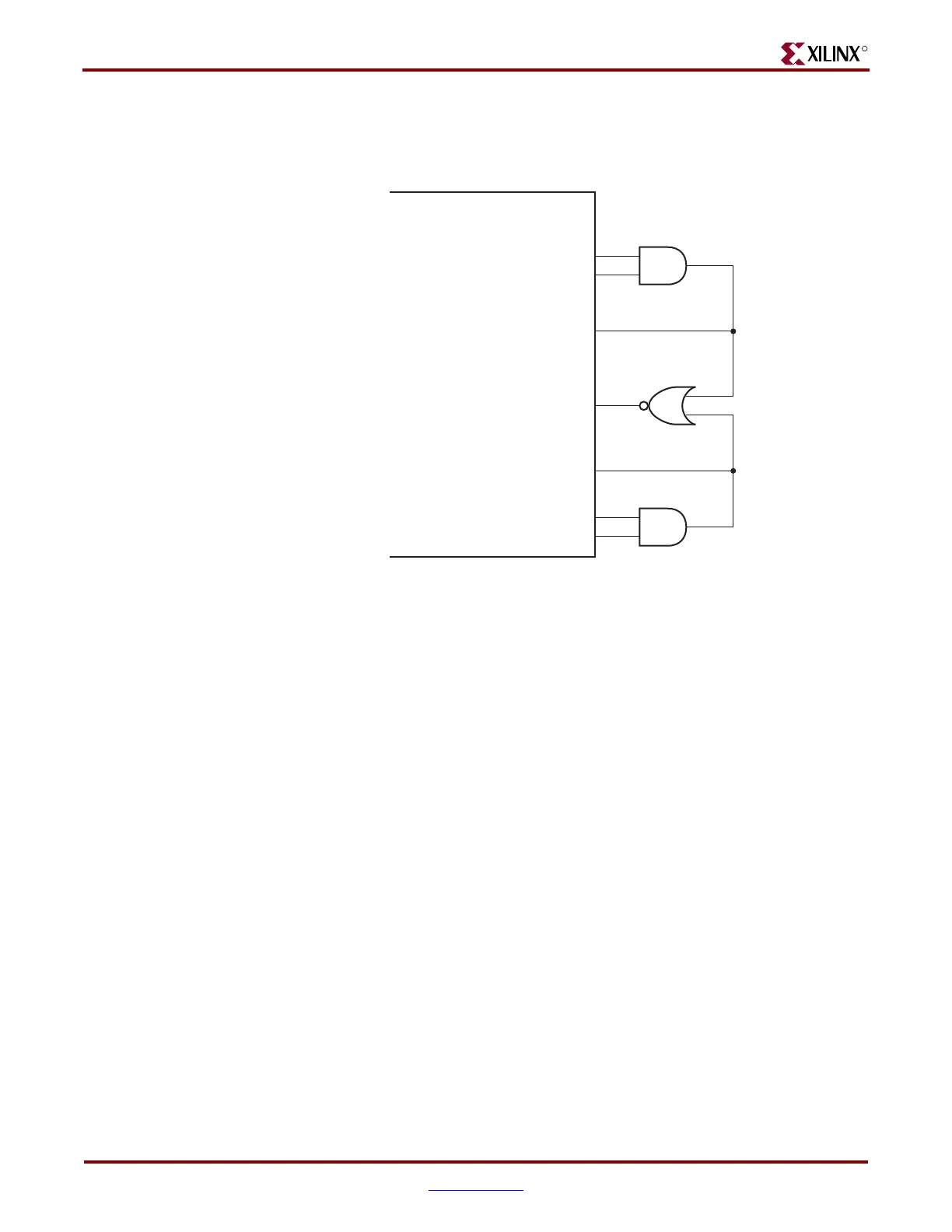

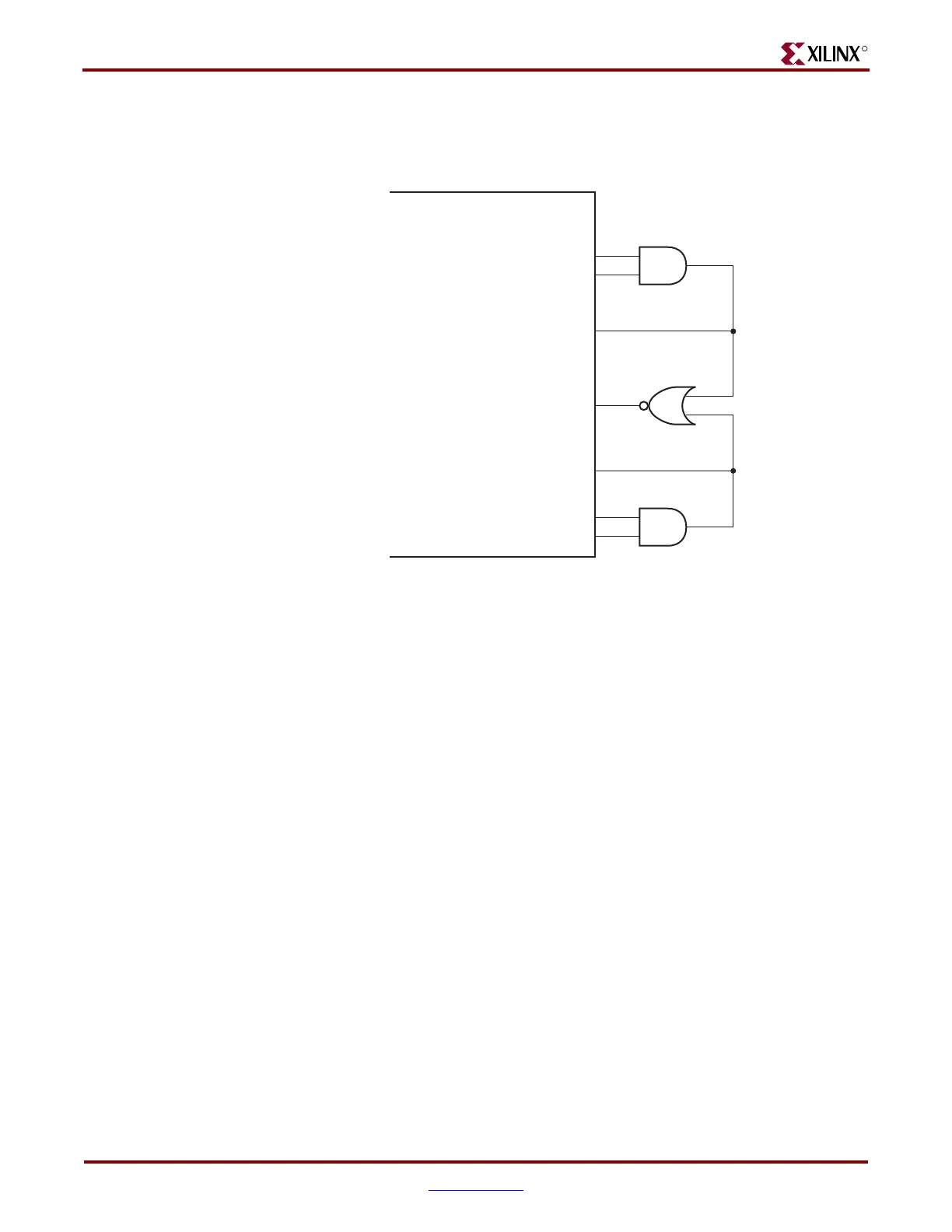

Figure 5-9 shows the link idle reset circuit required in all GTP designs. Because

RESETDONE is used in the circuit, TXUSRCLK, TXUSRCLK2, RXUSRCLK, and

RXUSRCLK2 must all be clocked on active GTP transceivers.

Note:

If a RXRECCLK is used to generate or derive any of the USRCLKs and an Electrical Idle

condition occurs, the derived USRCLKs will flatline, because RXRECCLK flatlines when the

generating CDR is in reset. In this case RXELECIDLE(0/1) can be used as a selection signal of a

BUFGMUX to multiplex between the RXRECCLK(0/1) and a different CDR independent clock source.

Figure 5-9: Link Idle Reset Implementation

RESETDONE0

RXELECIDLE0

RESETDONE1

RXELECIDLE1

RXELECIDLERESET0

RXELECIDLERESET1

GTP_DUAL Tile

UG196_c5_09_082806

RXENELECIDLERESETB

Loading...

Loading...