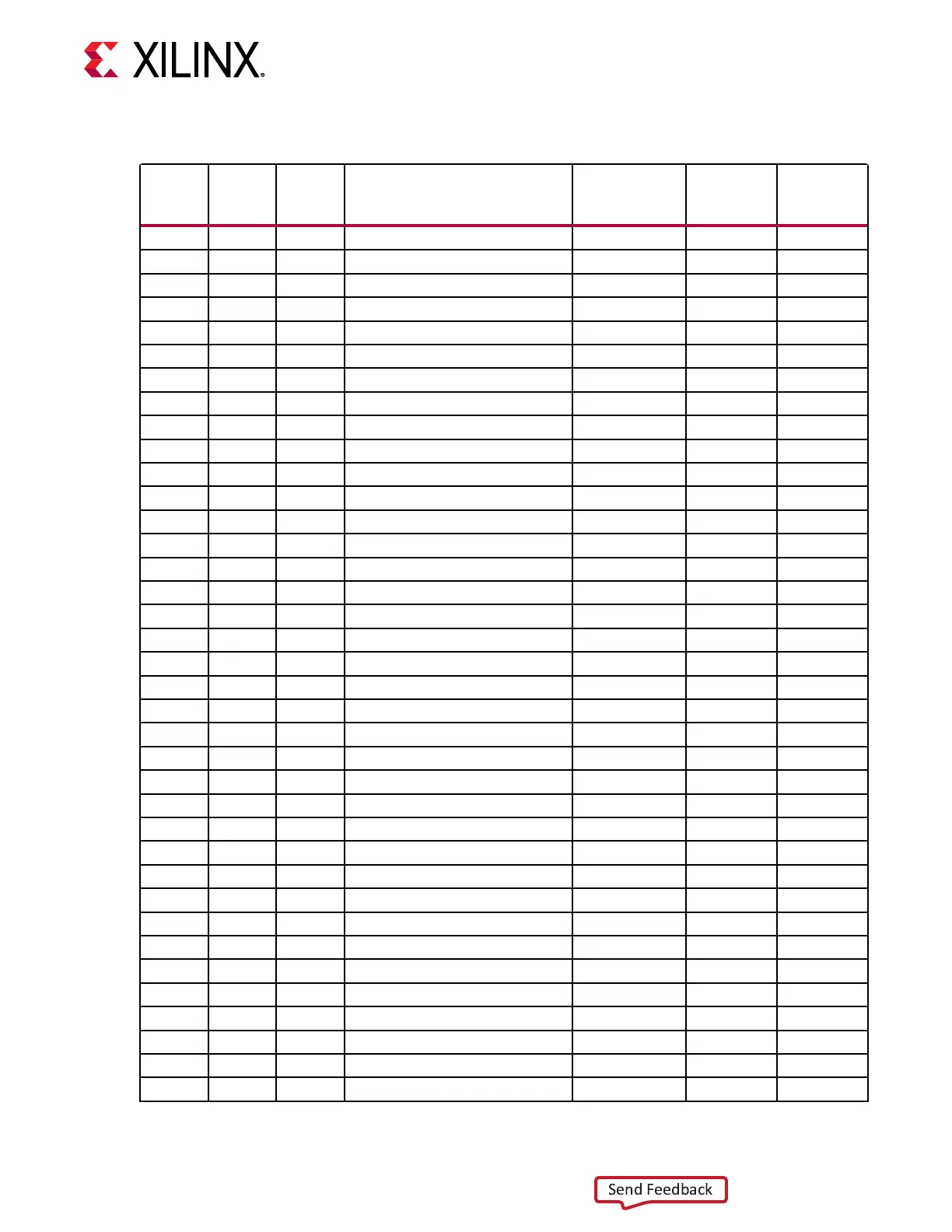

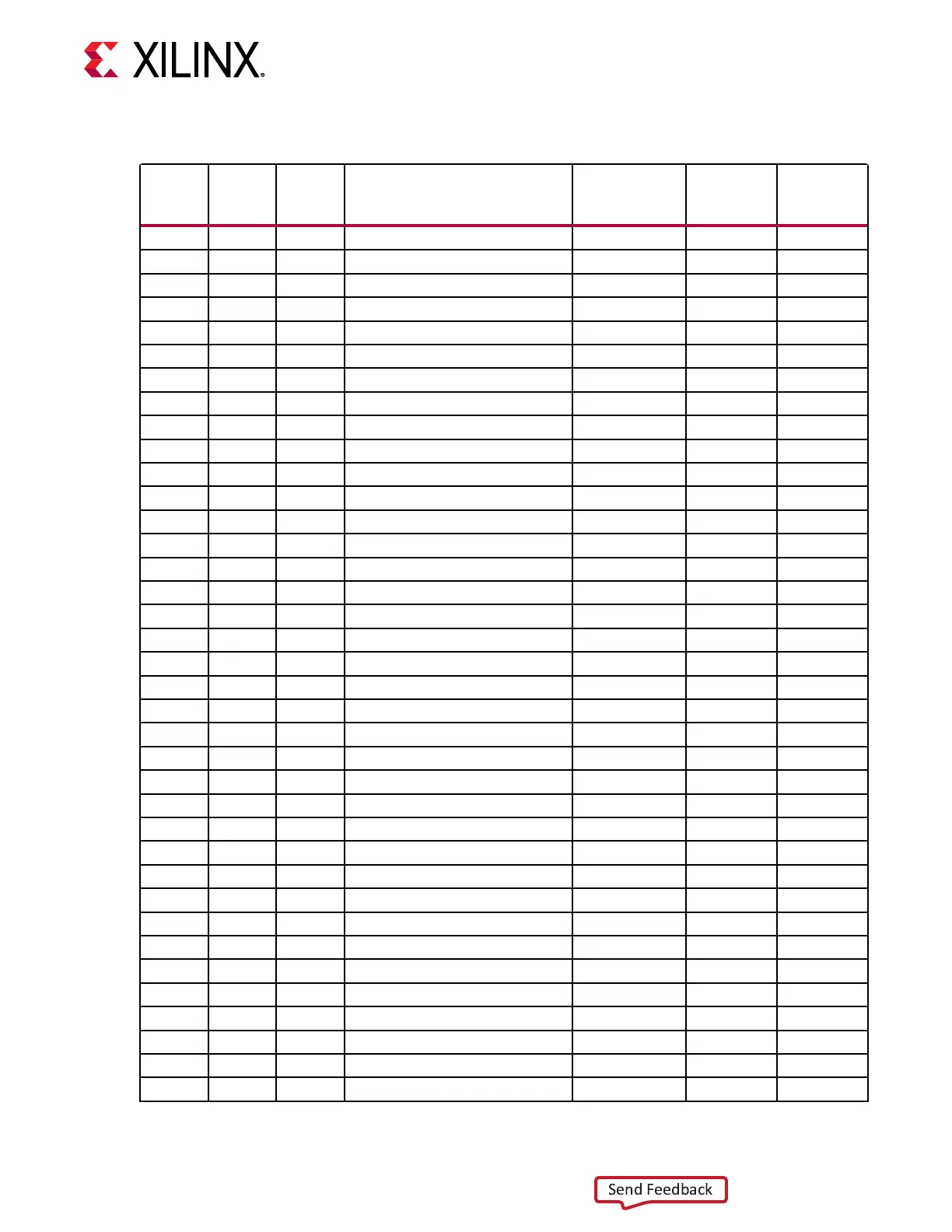

Table 75: DRP Map of GTM_DUAL Primitive (cont'd)

DRP

Addres

s

DRP

Bits

R/W Attribute Name Attribute Bits

Attribute

Encoding

DRP

Encoding

0x039 [15:0] R/W CH0_RX_APT_CFG11B [15:0] 0–65535 0–65535

0x03a [15:0] R/W CH0_RX_APT_CFG12A [15:0] 0–65535 0–65535

0x03b [15:0] R/W CH0_RX_APT_CFG12B [15:0] 0–65535 0–65535

0x03c [15:0] R/W CH0_RX_APT_CFG13A [15:0] 0–65535 0–65535

0x03d [15:0] R/W CH0_RX_APT_CFG13B [15:0] 0–65535 0–65535

0x03e [15:0] R/W CH0_RX_APT_CFG14A [15:0] 0–65535 0–65535

0x03f [15:0] R/W CH0_RX_APT_CFG14B [15:0] 0–65535 0–65535

0x040 [15:0] R/W CH0_RX_APT_CFG15A [15:0] 0–65535 0–65535

0x041 [15:0] R/W CH0_RX_APT_CFG15B [15:0] 0–65535 0–65535

0x042 [15:0] R/W CH0_RX_APT_CFG16A [15:0] 0–65535 0–65535

0x043 [15:0] R/W CH0_RX_APT_CFG16B [15:0] 0–65535 0–65535

0x044 [15:0] R/W CH0_RX_APT_CFG17A [15:0] 0–65535 0–65535

0x045 [15:0] R/W CH0_RX_APT_CFG17B [15:0] 0–65535 0–65535

0x046 [15:0] R/W CH0_RX_APT_CFG18A [15:0] 0–65535 0–65535

0x047 [15:0] R/W CH0_RX_APT_CFG18B [15:0] 0–65535 0–65535

0x048 [15:0] R/W CH0_RX_APT_CFG19A [15:0] 0–65535 0–65535

0x049 [15:0] R/W CH0_RX_APT_CFG19B [15:0] 0–65535 0–65535

0x04a [15:0] R/W CH0_RX_APT_CFG20A [15:0] 0–65535 0–65535

0x04b [15:0] R/W CH0_RX_APT_CFG20B [15:0] 0–65535 0–65535

0x04c [15:0] R/W CH0_RX_APT_CFG21A [15:0] 0–65535 0–65535

0x04d [15:0] R/W CH0_RX_APT_CFG21B [15:0] 0–65535 0–65535

0x04e [15:0] R/W CH0_RX_APT_CFG28A [15:0] 0–65535 0–65535

0x04f [15:0] R/W CH0_RX_APT_CFG28B [15:0] 0–65535 0–65535

0x050 [15:0] R/W CH0_RX_APT_CFG22A [15:0] 0–65535 0–65535

0x051 [15:0] R/W CH0_RX_APT_CFG22B [15:0] 0–65535 0–65535

0x052 [15:0] R/W CH0_RX_APT_CFG23A [15:0] 0–65535 0–65535

0x053 [15:0] R/W CH0_RX_APT_CFG23B [15:0] 0–65535 0–65535

0x054 [15:0] R/W CH0_RX_APT_CFG24A [15:0] 0–65535 0–65535

0x055 [15:0] R/W CH0_RX_APT_CFG24B [15:0] 0–65535 0–65535

0x056 [15:0] R/W CH0_RX_APT_CFG25A [15:0] 0–65535 0–65535

0x057 [15:0] R/W CH0_RX_APT_CFG25B [15:0] 0–65535 0–65535

0x058 [15:0] R/W CH0_RX_APT_CFG26A [15:0] 0–65535 0–65535

0x059 [15:0] R/W CH0_RX_APT_CFG26B [15:0] 0–65535 0–65535

0x05a [15:0] R/W CH0_RX_APT_CFG27A [15:0] 0–65535 0–65535

0x05b [15:0] R/W CH0_RX_APT_CFG27B [15:0] 0–65535 0–65535

0x05c [15:0] R/W CH0_RX_DSP_CFG [15:0] 0–65535 0–65535

0x064 [15:0] R/W CH0_RX_CAL_CFG2A [15:0] 0–65535 0–65535

Appendix A: DRP Address Map of the GTM Transceiver in UltraScale+ FGPAs

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 135

Loading...

Loading...