ZCU111 Board User Guide 41

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Chapter 3: Board Component Descriptions

The connections between the USB 2.0 PHY (U12) and the XCZU28DR RFSoC PS bank 502 are

referenced in Appendix B, Xilinx Design Constraints.

GEM3 Ethernet (MIO 64-77)

The PS-side Gigabit Ethernet MAC (GEM) implements a 10/100/1000 Mb/s Ethernet

interface (see Figure 3-10), which connects to a TI DP83867IRPAP Ethernet RGMII PHY

before being routed to an RJ45 Ethernet connector. The RGMII Ethernet PHY is boot

strapped to PHY address 5'b01100 (0x0C) and Auto Negotiation is set to Enable. The

communication with the device is described in the DP83867 RGMII PHY data sheet [Ref 20].

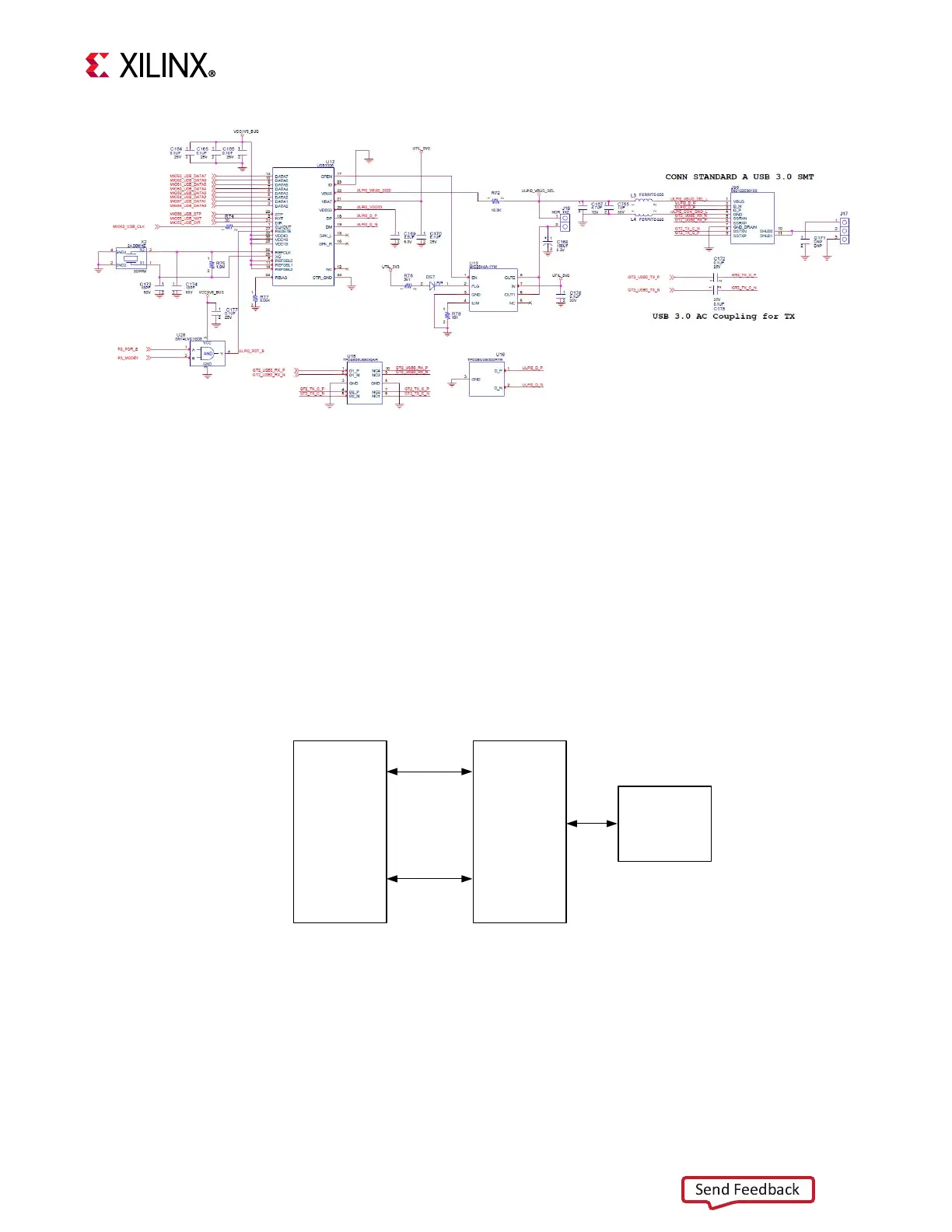

X-Ref Target - Figure 3-9

Figure 3-9: USB3320 ULPI Transceiver Circuit

X-Ref Target - Figure 3-10

Figure 3-10: Ethernet Block Diagram

GEM

MIO

RGMII

MDIO

TI

DP83867IR

RJ45 and

Magnetics

X20534-062118

Loading...

Loading...