560 Chapter 16

W-CDMA Uplink Digital Modulation for Receiver Test

W-CDMA Uplink Concepts

PRACH Mode

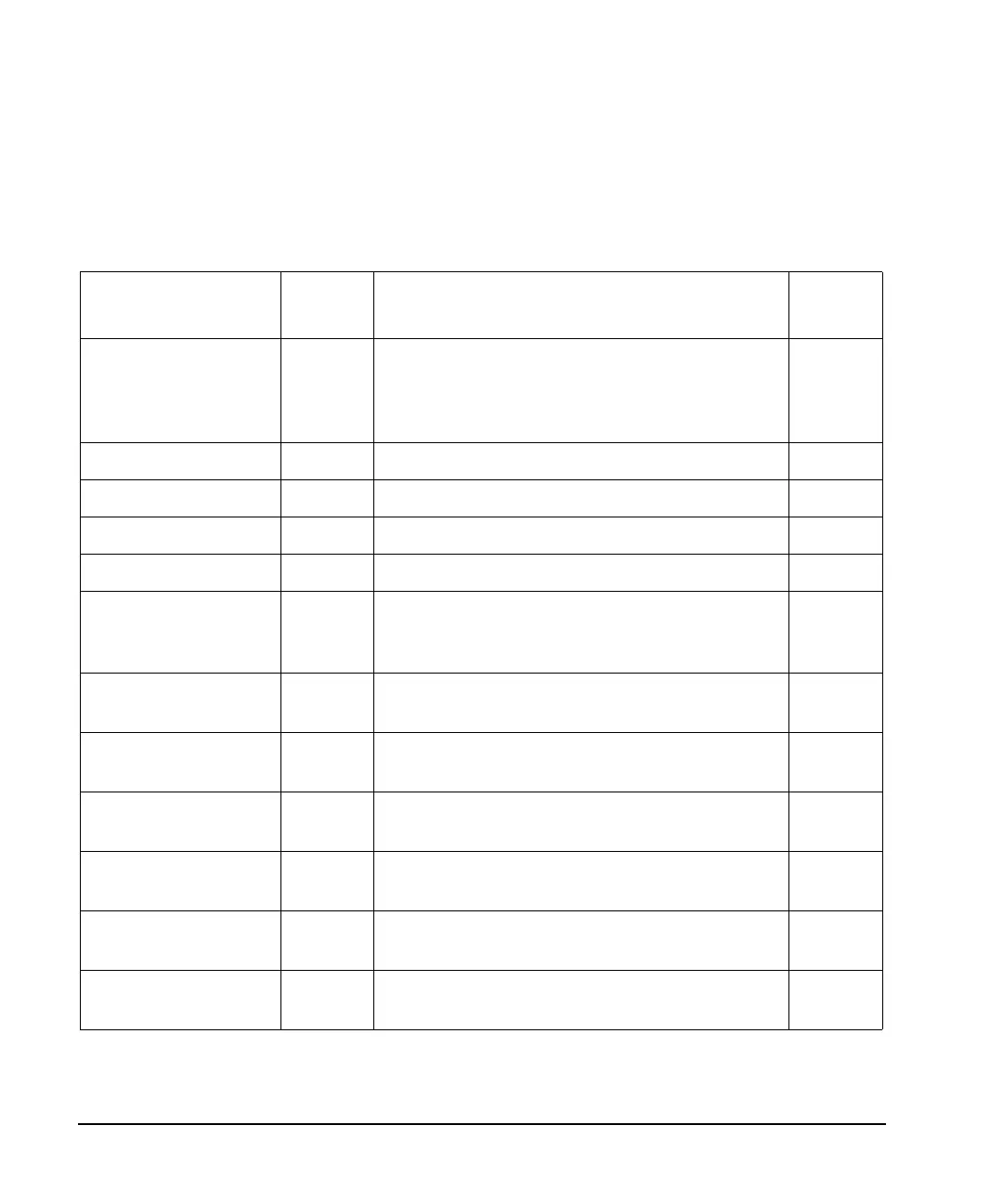

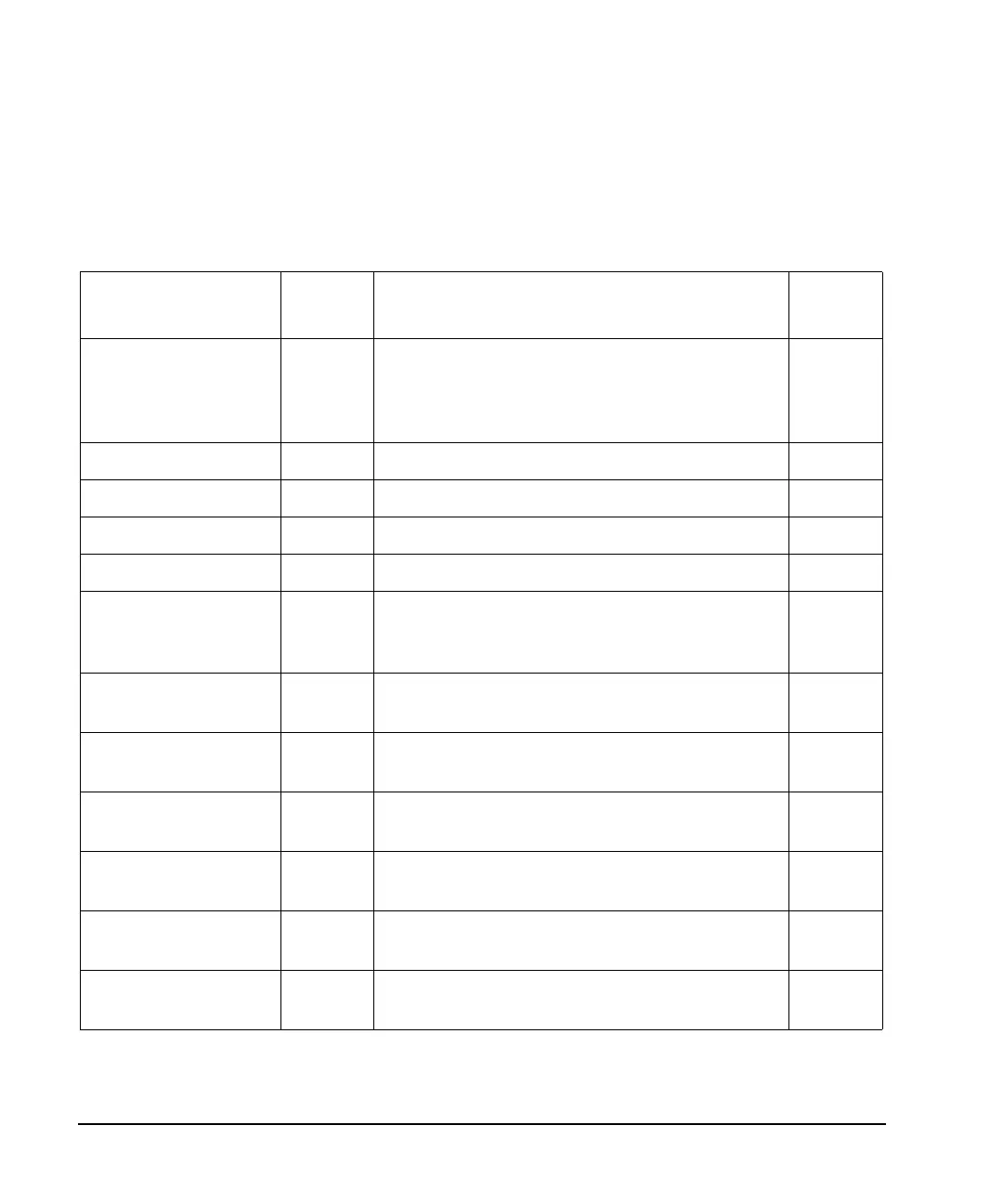

Table 16-8 provides descriptions for fixed and user-selectable signals available in PRACH mode. Figure

16-77 on page 561 shows an example of PRACH output timing alignment.

Table 16-8 Signal Descriptions for PRACH Mode

Signal Label Input/

Output

Signal Description SCPI

Syntax

Frame Sync Trigger Input The input signal can be set to either the frame clock

or the system frame number SFN) reset signal by

toggling the

Sync Source FClk SFN softkey. The frame

clock can be set to 10, 20, 40, 80, or 2560 ms.

FSYN

PRACH Start Trigger Input Trigger to start PRACH. PSTR

AICH Trigger Input Trigger to start AICH. AITR

None Output No signal. RPS0

Chip Clock Output Chip clock. 3.84 MHz is the default setting. RPS1

Trigger Sync Reply

(system sync output)

Output Response pulse of the frame sync trigger. The frame

sync trigger reply indicates how much frame

alignment was necessary.

RPS7

Preamble Raw Data Output Preamble data after 2nd interleaver (before

spreading and scrambling).

RPS15

Preamble Raw Data

Clock

Output The clock for preamble raw data. RPS16

Message Data Raw

Data

Output The data for the message data part after 2nd

interleaver (before spreading and scrambling).

RPS11

Message Ctrl Raw Data Output The data for the message control part after 2nd

interleaver (before spreading and scrambling).

RPS13

Message Data Raw

Data Clock

Output The clock for the message data part raw data. RPS12

Message Ctrl Raw Data

Clock

Output The clock for the message control part raw data. RPS14

Loading...

Loading...