7 - 8

MELSEC-Q

7 MEMORY CONFIGURATION AND DATA PROCESS

7.2 Data transmission process

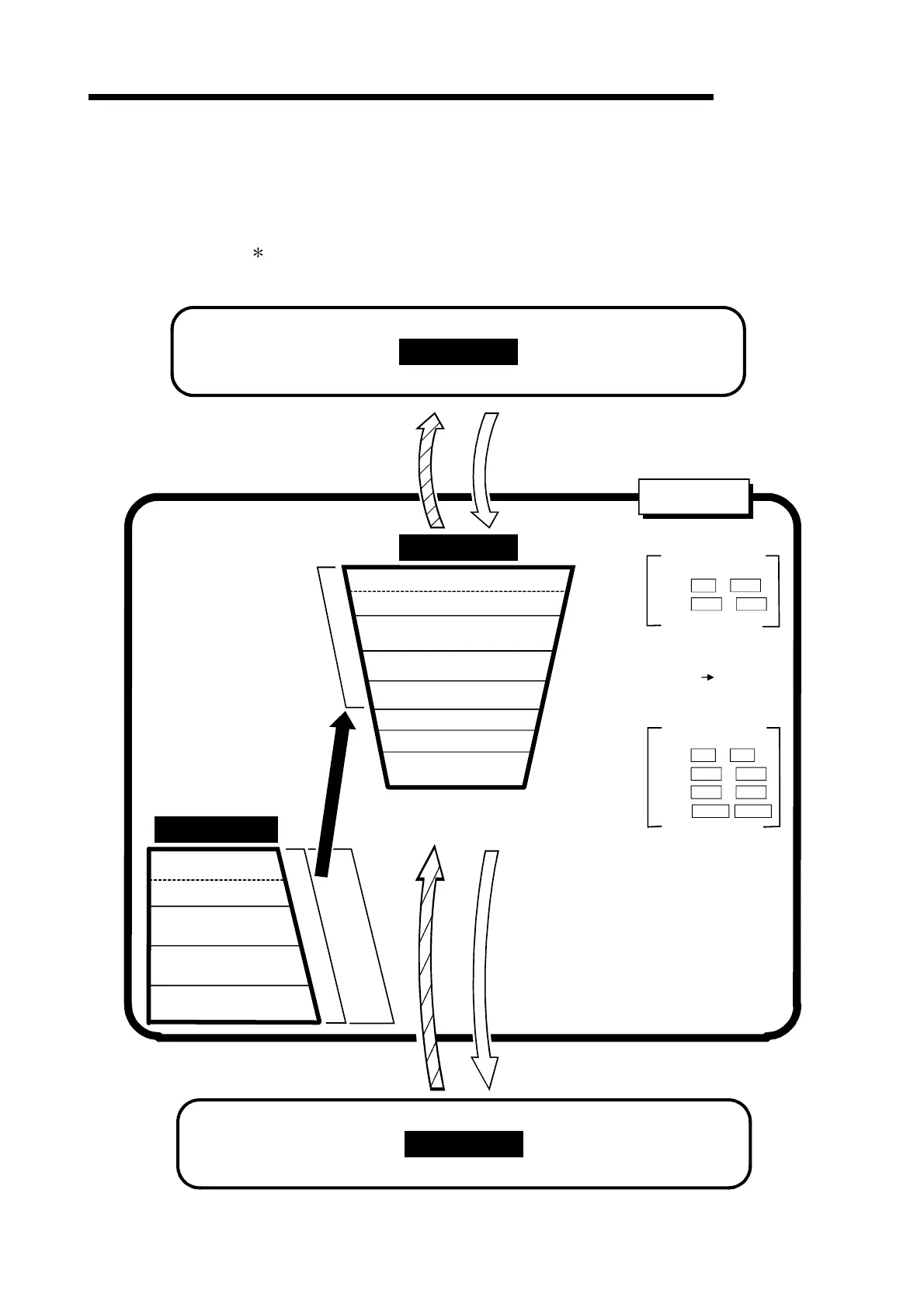

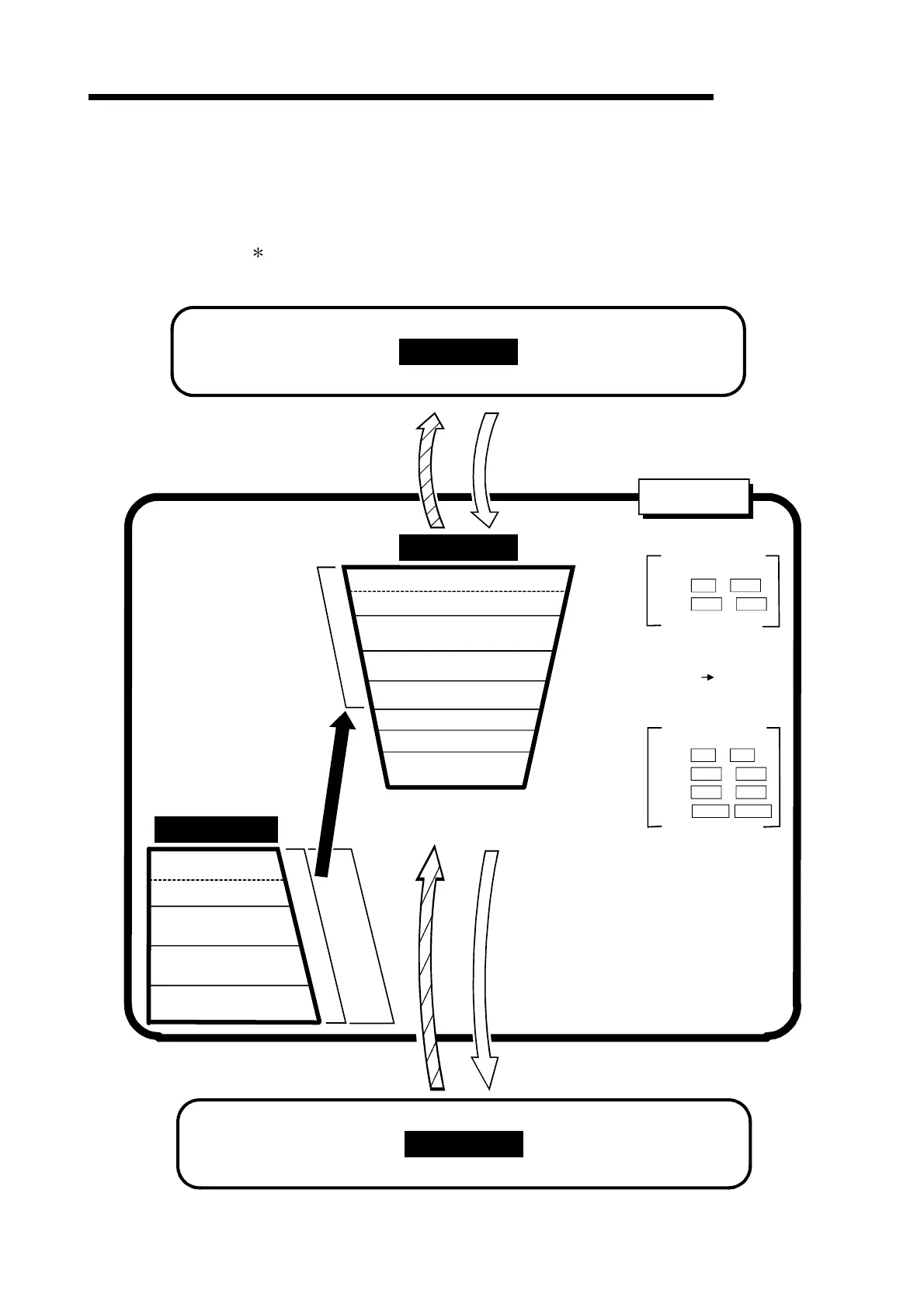

The data is transmitted between the QD75 memories with steps (1) to (10) shown

below.

The data transmission patterns numbered (1) to (10) on the right page correspond to

the numbers (1) to (10) on the left page.

ROM

(3) PLC READY signal

[Y0] OFF ON

Pr.10

Pr.8

to

Pr.25

Pr.42

(5) Servo amplifier read

Servo amplifer

Pr.7Pr.1

Pr.11 Pr.24

Pr.43 Pr.57

Pr.200

Pr.201

(2) Valid upon execution of

the TO instruction.

For PLC READY signal ON : Valid

Parameter area (a)

Parameter area (b)

Positioning data area

(No.1 to

600)

Block start data area

(No.7000 to 7004)

PLC CPU

memo area

Monitor data area

Control data area

Buffer memory

(1) Power supply ON/

PLC CPU reset

(2) TO command(4) FROM command

QD75

PLC CPU

Parameter area (a)

Parameter area (b)

Positioning data area

(No.1 to

600)

Block start data area

(No.7000 to 7004)

Flash ROM

Servo parameter area

(No.30100 to 30499)

Servo parameter area

(No.30100 to 30499)

Parameter area (a)

Parameter area (b)

to

to

to

to

Loading...

Loading...