CPU 31x-2 as DP Master/DP Slave and Direct Communication

2-11

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

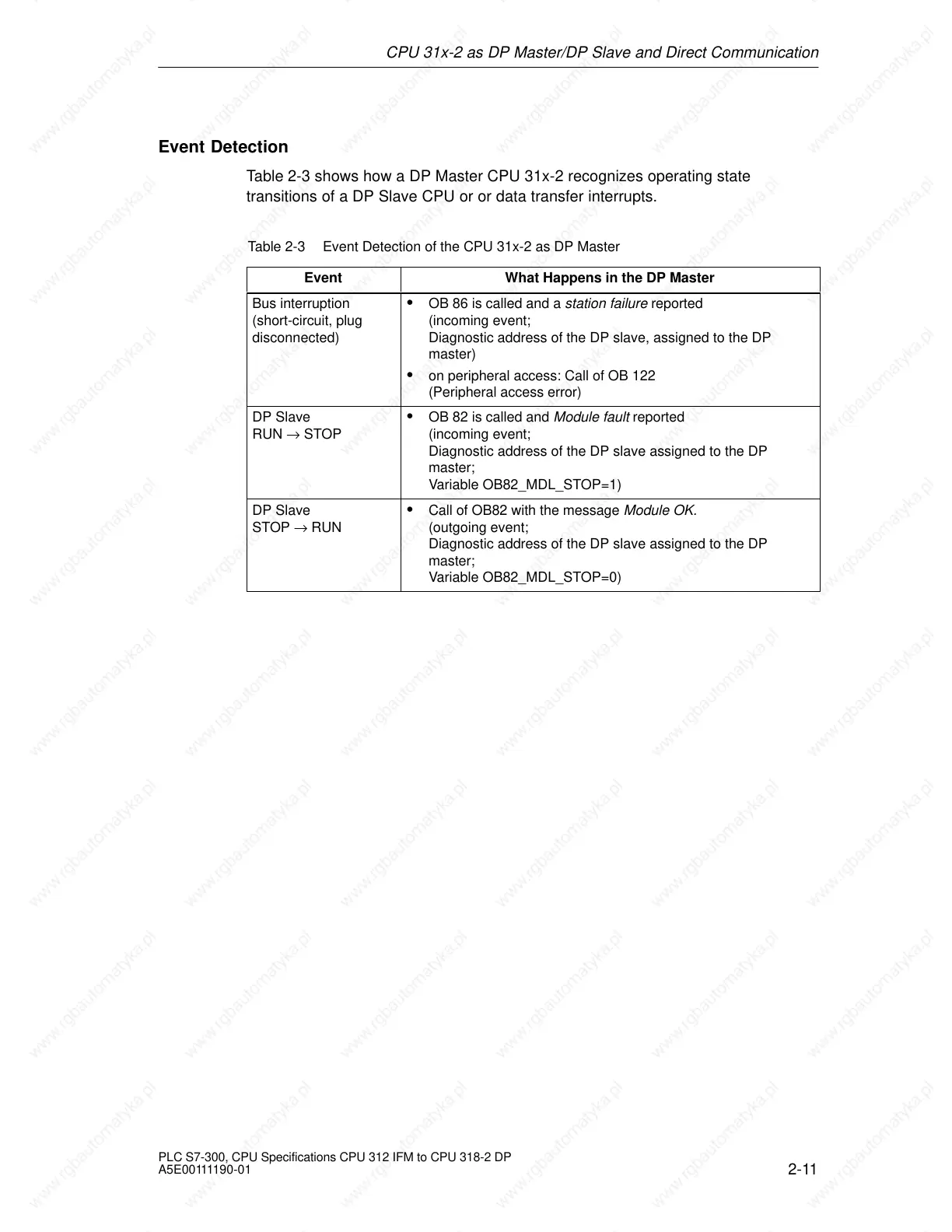

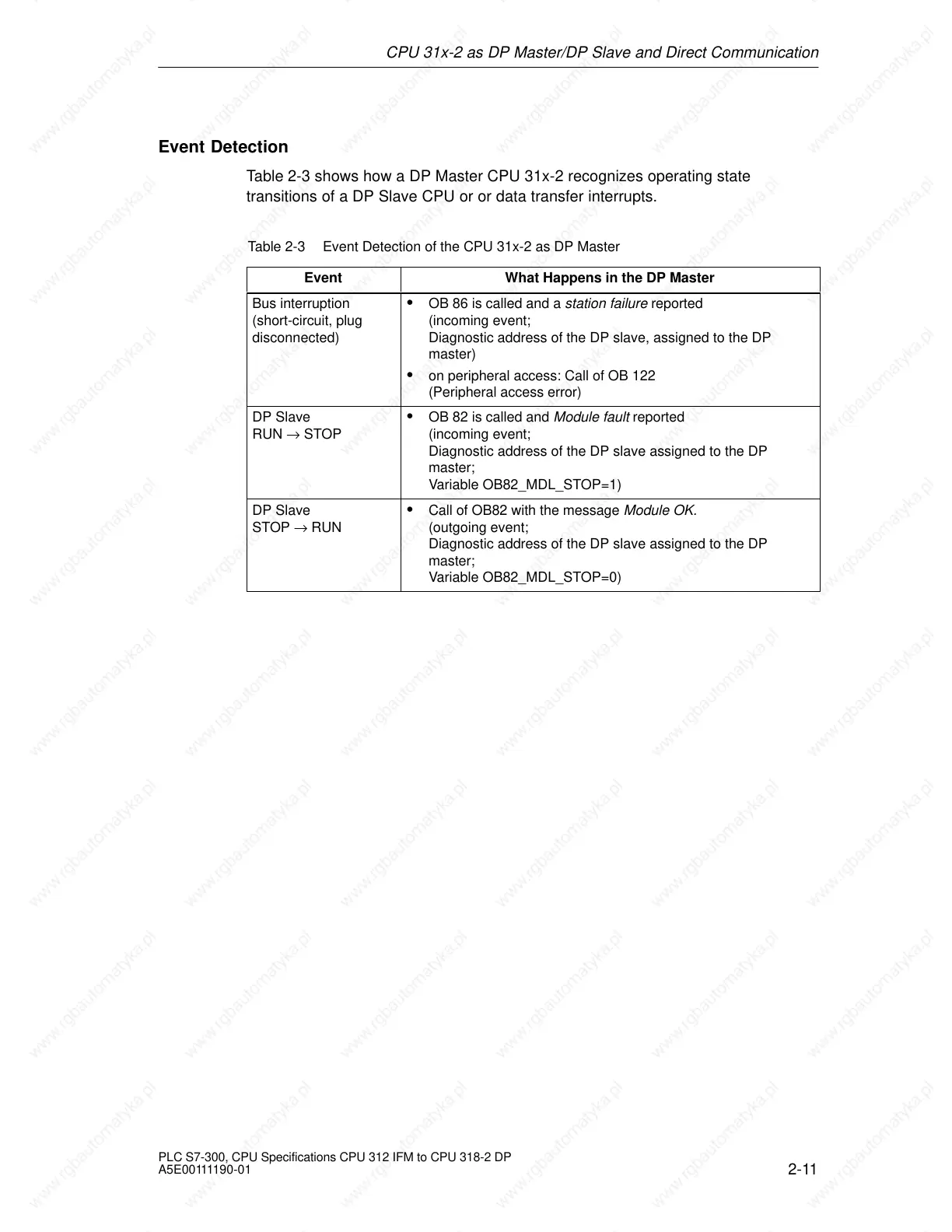

Event Detection

Table 2-3 shows how a DP Master CPU 31x-2 recognizes operating state

transitions of a DP Slave CPU or or data transfer interrupts.

Table 2-3 Event Detection of the CPU 31x-2 as DP Master

Event

What Happens in the DP Master

Bus interruption

(short-circuit, plug

disconnected)

OB 86 is called and a station failure reported

(incoming event;

Diagnostic address of the DP slave, assigned to the DP

master)

on peripheral access: Call of OB 122

(Peripheral access error)

DP Slave

RUN → STOP

OB 82 is called and Module fault reported

(incoming event;

Diagnostic address of the DP slave assigned to the DP

master;

Variable OB82_MDL_STOP=1)

DP Slave

STOP → RUN

Call of OB82 with the message Module OK.

(outgoing event;

Diagnostic address of the DP slave assigned to the DP

master;

Variable OB82_MDL_STOP=0)

Loading...

Loading...